基于FPGA的VXI总线寄存器基模块接口电路设计(06-100)

开机初始化

本文引用地址://m.amcfsurvey.com/article/81437.htm根据VXI总线时序,在电源接通后,背板总线上SYSRST信号由低变高,以使SOFTRST信号由高变低并启动一次模块复位自检过程。根据VXI总线协议,模块复位自检应包括各寄存器(基本配置寄存器和用户定义操作寄存器)的初始化和功能电路的初始化。

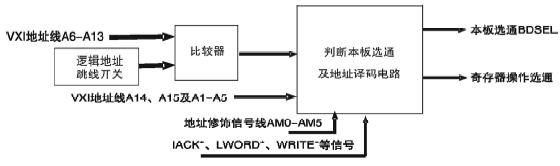

模块和寄存器译码

一个VXIbus系统中最多可有256个器件,每个器件都有一个唯一的逻辑地址,编号从0到255。通常规定00H逻辑地址赋予插入0号槽的为系统提供公共资源的资源管理器和0号槽器件,而FFH号在上电时赋予系统的所有DC器件,其它的01H--FEH号分配给任意的SC器件。每个器件的逻辑地址由人工通过“逻辑地址选择器”设定。器件选通是由VXI的地址线A6-A13和地址修改线AM0-AM5来共同实现的,具体原理如图2所示。逻辑地址作为该器件的标准组态/操作寄存器的基地址。每个VXIbus器件有一组64字节的标准组态/操作寄存器位于系统A16寻址空间的高16K字节。VXIbus系统中,各器件内部的各可寻址单元是统一分配的。每个器件都支持16位寻址方式,每个器件64字节的最小地址空间是在寄存器基地址的基础上向上叠加的,如果器件的逻辑地址为V,则器件寄存器的基地址可由下式给出:

器件寄存器的基地址=215+214+V×64

选中模块的条件用逻辑表达式描述为

CARDADDR=(A[13..6]=LA[7..0])&&(AM [5..0]=2DH||A M[5..0]=29H)&&(IACK* =1)&&(LWORD*=1),也可用语言描述为:当器件被寻址时,接收地址线A01-A15及地址修改线AM0-AM5上的信息,并将其与本模块上硬件地址开关设置的逻辑地址相比较,如果AM0-AM5上的逻辑值为29H或2DH,地址线A15,A14均为1,并且A13-A6上的逻辑值与模块的逻辑地址相等时,该器件被选通,接着其译码结果被送往下一级译码控制,通过对地址A01-A05进行译码选中模块在16位地址空间的操作寄存器。

评论