利用Virtex-5 FPGA实现最低功耗解决方案

除了因工艺尺寸缩小到65纳米所致固有的35~40%动态功耗降低外,Virtex-5器件的架构创新还能进一步降低每个设计的功耗。大多数可增加动态 功耗的结点电容,是由逻辑单元间的互连线引起的。新型Virtex-5架构从以下方面减小了连线电容:

本文引用地址://m.amcfsurvey.com/article/84173.htmVirtex-5的可配置逻辑模块(CLB)是基于6输入查找表(6-LUT)逻辑结构的,在以前的器件中是使用4输入查找表。这意味着在每个LUT中能够实现更多的逻辑,相当于较少的逻辑级,从而降低了对逻辑单元之间大电容连线的需求。

Virtex-5的互联结构目前包括了对角线对称的连线,意味着每个CLB与所有相邻的模块(包括处于对角线位置的模块)之间都有直接的“单一”连接。当逻辑功能之间需要连接时,这一连接更有可能成为总电容最小的“单一”连接,而以往的互联结构对于相同的连接问题可能会需要两个或更多结点。

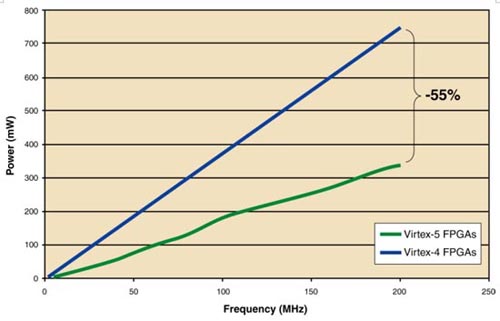

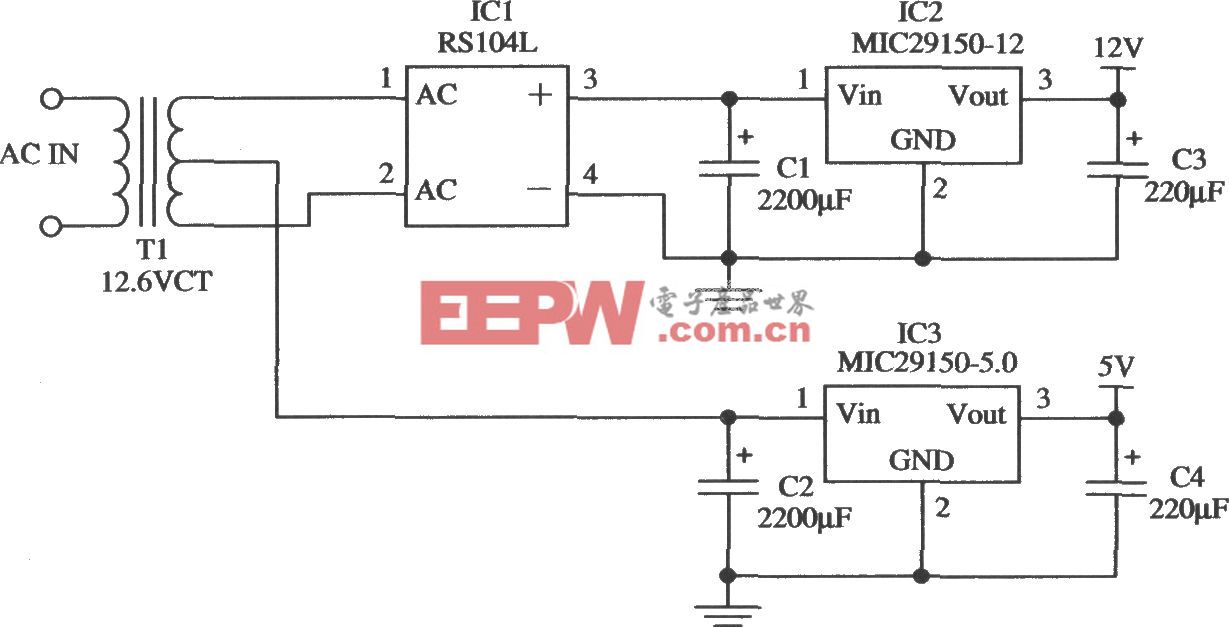

6-LUT结构和改进的互联模式,通过降低平均结点电容来降低核心动态功耗,效果远远超过仅使用65纳米工艺所带来的改进。图2显示了来自标准设计的核心动态功耗的测量结果,其中每个Virtex-5器件和Virtex-4器件中都有1,024个8位计数器。这些实际的测量结果显示,工艺和结构上的共同优化所带来的动态功耗的降低超过了50%。

图2: Virtex-4与Virtex-5FPGA中的基准计数器设计动态功耗比较。

硬IP模块

Virtex-5器件中所包含的硬IP模块(专门用来实现一些常用功能的电路)数量,超过业界其他任何一款FPGA。相比使用通用FPGA逻辑而言,使用搭载这些模块的FPGA设计来实现相同功能,可进一步降低功耗。

与FPGA结构不同,这些专用模块中只含有为实现所要求功能而必需的晶体管,并且没有可编程的互联,因此互联电容最小。较少的晶体管和较小的结点电容能降低静态和动态功耗。因而这些专用模块在实现相同功能的同时,功耗只有采用通用FPGA结构的十分之一。

除了增加新型的专用模块之外,Virtex-4器件中融合的很多模块,在Virtex-5器件中都被重新设计,以增加新的特性,提高性能并降低功耗。例如,Virtex-4系列中18Kb的block RAM存储器在Virtex-5器件中被增加到了36Kb;每个block RAM能被分成两个独立的18Kb的存储器,以便向下兼容Virtex-4的设计。

有趣的是,从功耗的角度来看,每个18Kb的子模块由两个9Kb的物理存储阵列构成。对于大多数block RAM配置,任何对block RAM的读写请求一次只需要访问9Kb物理存储器中的一个。因此其余的9Kb存储器能在不被访问时可有效地“关断”。在过渡至65纳米工艺所带来的功耗降低的基础上,这种结构又使功耗进一步降低了50%。这一对于9Kb模块的乒乓式存取是新型block RAM结构所固有的,这就意味着使用这项功能不需要用户或软件来进行控制。它能动态并自动地进行,使所有使用block RAM的设计降低了大量的功耗,并且不会影响模块的性能。

Virtex-5器件中专用的DSP元件也进行了大量的改进,以实现更多的功能,提高性能并降低功耗。在片与片的功耗比较中,新型的Virtex-5 DSP片比Virtex-4 DSP片降低了大约40%。这主要归功于前面所讨论的65纳米工艺中电压和电容的减小。

然而,由于Virtex-5 DSP片具有更强的功能和更广泛的接口,许多DSP运算通过利用这些附加的功能进一步降低了功耗。在许多情况下,当使用新型DSP片的全部功能时,总功耗最高可降低75%。即使你不是在设计一个DSP产品,也能使用DSP片来实现标准的逻辑功能(计数器、加法器、桶式移位器),这样会比在标准FPGA逻辑中实现同样的功能节省功耗。

最后介绍经过改进的专用模块——Virtex-5系列的LXT平台,其中包括了几吉位的串行收发机,能以高达3.125Gbps的速率工作。这些“SERDES”模块在实现时着重考虑了低功耗需求。每个Virtex-5 LXT器件中的全双工收发机在3.125Gbps的速度下的总功耗小于100mW,与Virtex-4串行收发机相比降低了大约75%。

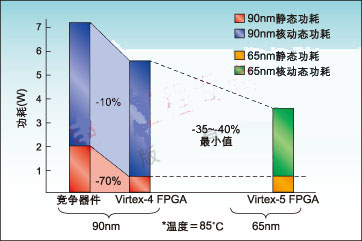

与Virtex-4系列产品一样,Virtex-5器件也采用了一系列工艺和架构上的革新,力求在提供尽可能低的功耗的同时,仍然使性能提高30%或更多。如图3所示,Virtex-5系列产品的静态功耗与Virtex-4器件相当,但比竞争性FPGA具有明显的优势。

图3:典型设计中现有FPGA器件的功耗比较。

Virtex-5器件核心的动态功耗比市场上其高性能FPGA低至少35~40%。新型6-LUT和对角线对称的互联等架构上的革新,使实际核心动态功耗进一步降低了50%或以上。此外,利用改进的专用模块也进一步降低了功耗。

评论