基于FPGA的通信系统基带验证平台的设计

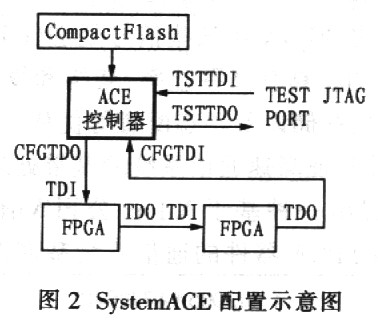

SystemACE配置示意图如图2所示。完成FP-GA设计后,通过软件生成所设计的下载配置文件,通过CF卡读写器将文件置于CF存储卡中。当平台上电后,ACE控制器读取CF卡中的配置文件,通过JTAG链将数据下载到各FPGA,完成自动配置。也可以通过JTAG下载电缆连接TEST JTAG接口,直接对FPGA进行在线配置。

本文引用地址://m.amcfsurvey.com/article/85609.htm

3.2 时钟电路和复位及电压监视电路

本平台采用两个相互独立的有源晶体振荡器提供20 MHz时钟,分别作为接收机和发射机的时钟源。由于板上多处地方需要20 MHz时钟(如ADC和DAC),而仅靠晶体振荡器供给时钟除导致驱动力较弱外,还可能会产生较大时钟偏移或抖动。选用时钟驱动器IDT74FCT38074为系统提供时钟,这是一款3.3 V供电,CMOS工艺的1驱4时钟驱动器,输入时钟最高为166 MHz,同时提供4路低偏移同相时钟。通过两片IDT74FCT38074,分别为接收机和发射机各个模块提供精确时钟。输入时钟进入FPGA后又可以通过DCM的分频倍频处理,为FP-GA内部各个功能模块提供所需的时钟。

在Virtex-Ⅱ器件内部,所有DCM模块通过时钟多路复用器逻辑分配到器件内部。所提供的16个全局时钟缓冲器可实现16个时钟域的控制,保证了DCM模块的时钟输出具有最小的传输延迟(Skew)。

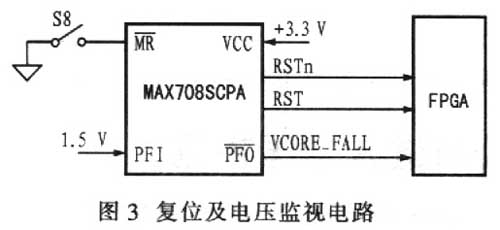

复位及电压监视电路采用MAX708SCPA,提供上电自动复位及手动复位。MAX708SCPA的PFI引脚为监视电压输入端,当PFI输入电压低于1.25 V时,PFO引脚输出低电平表示电压过低,本设计中用于监视FPGA 1.5 V内核电压。开关按钮S8提供手动复位。其电路示意图如图3所示。

3.3 数模和模数转换电路

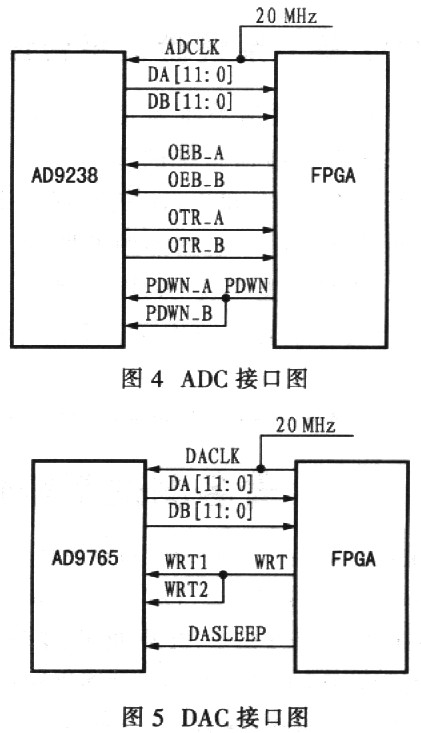

本平台用于验证通信基带系统,需要将发射机输出的I路、Q路信号通过数模转换器(DAC)转换成模拟信号,接收机则通过模数转换器(ADC)将接收信号转换成数字信号。本平台设计采用的ADC和DAC分别为ADI公司的AD9238和AD9765。

AD9238是双通道12位ADC。速度等级分为20MS/s、40MS/s和65MS/s。功耗为180mW~600mW,适用于要求低功耗和较小PCB面积的应用。AD9238的信噪比(SNR)为70 dB,无杂散信号动态范围(SFDR)为85 dBc。带有片内宽带差分采样保持放大器(SHA),允许用户选择多种输入范围和失调电压,包括单端输入。AD9765是双端口、高速率、双通道、12 bit的CMOS数模转换器(DAC)。它集成了2个高性能的12 bit TxDAC。更新速率可达125 MS/s,无杂散信号动态范围(SFDR)为75 dBc,O.1%的增益偏移匹配率。输出为差分电流、满幅度为20mA。

本设计中,AD9238工作在2Vp-p差分工作模式,采用内部参考电压,两通道工作在共享电压参考模式。输入差分幅度为2 V。信号时钟输入可以采用时钟驱动器的20MHz输出或由FPGA提供,最高采样率为40 MS/s。AD9238的两通道选择AD8138作为运放驱动器,为ADC提供差分输入信号。AD9765工作在双端口模式,两通道增益控制可分别调整,采用内部l.2 V参考电压。时钟输入也可以采用时钟驱动器的20 MHz输出或由FPGA提供。AD9238和AD9765与FPGA的连接示意图分别如图4和图5所示。

3.4 电源电路

本系统正常工作需要两种供电电压。一种为FPGA器件的内核电压1.5 V;另一种为FPGA器件的输入输出接口电压3.3 V,该电压同时还用于其他器件供电。

本设计采用适合FPGA应用的低电压、大电流线性稳压器(LDO)供电方案。电源输入采用标准的ATX电源接口,可以由ATX电源供电,其中+12 V输入直接给风扇供电,用于FPGA散热。+5 V输入通过Tl公司的TPS75533和TPS75415分别转换为3.3 V和l.5 V电压输出。TPS75533是一款最低压差可为250 mV的LDO,可提供3.3 V,5 A输出。TPS75415可提供1.5 V,2 A输出,其快速瞬态响应可有效改善系统性能。LDO采用线性调节原理,输出纹波很小,外围电路简单,只要求外接输入和输出电容即可工作。缺点是电压转换效率不高,发热量大,对散热控制方面要求较高。TPS75533采用TO-220封装,可以通过背部散热片有效散热,而TPS75415采用PowerPADTM的TSSOP小封装,在提供2W散热功率,提高散热性的同时节省了占用面积。

3.3 V和1.5 V电压之间加稳压二极管和肖特基二极管构成的保护电路,保证FPGA的内核电压与接口电压之差在一定范围内,防止器件损坏。

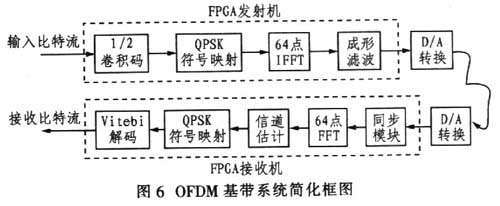

4 OFDM基带系统验证平台设计

基于FPGA的通信系统基带设计验证平台非常适用于高速无线通信系统的基带设计。采用该平台可验证基于IEEE 802.1la的OFDM基带系统的简化原型设计。设计框图如图6所示。

经验证,该平台能实现OFDM原型机的发送和接收功能,并能有效验证同步和信道估计算法的实际性能。

5 结束语

基于FPGA的通信系统基带设计验证平台采用大容量、高性能的FPGA器件,为通信系统的基带设计提供了一个有效的硬件实现平台。基于FPGA的实现和验证与计算机仿真相结合,将大大加速通信系统基带部分的快速原型设计,极大地方便了对实时性和运算量有较高要求的各类算法的验证。

评论