LVDS电路的仿真与设计

——

LVDS电路的仿真与设计

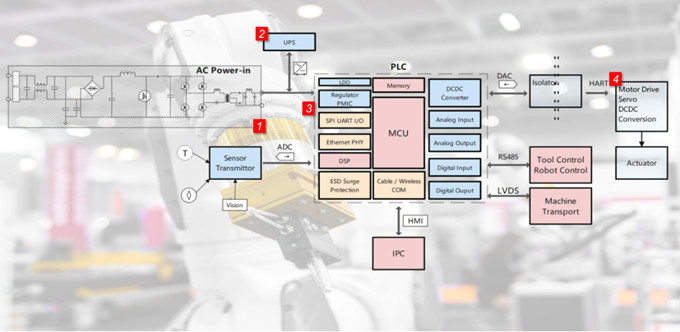

引言:随着电子设计技术的不断进步,要求更高速率信号的互连。在传统并行同步数字信号的数位和速率将要达到极限的情况下,设计师转向从高速串行信号寻找出路。HyperTansport(by AMD), Infiniband(by Intel),PCI-Express(by Intel)等第三代I/O总线标准(3GI/O)不约而同地将低压差分信号(LVDS)作为下一代高速信号电平标准。本文将从LVDS信号仿真、设计,测试等多方面探讨合适的LVDS信号的实现。

关键词:LVDS,阻抗控制,端接匹配

LVDS(Low Voltage Differential Signal)低压差分信号,最早由美国国家半导体公司(National Semiconductor)提出的一种高速串行信号传输电平,由于它传输速度快,功耗低,抗干扰能力强,传输距离远,易于匹配等优点,迅速得到诸多芯片制造厂商和应用商的青睐,并通过TIA/EIA(Telecommunication Industry Association/Electronic Industries Association)的确认,成为该组织的标准(ANSI/TIA/EIA-644 standard)。LVDS信号被广泛应用于计算机、通信以及消费电子领域,并被以PCI-Express为代表的第三代I/O标准中采用。

传输线阻抗设计

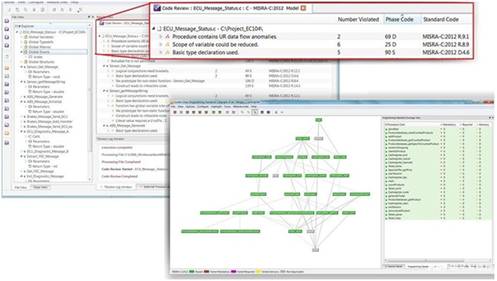

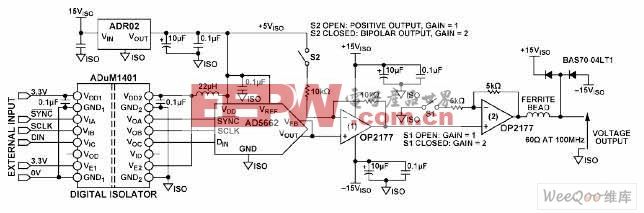

LVDS信号的电压摆幅只有350MV, 为电流驱动的差分信号方式工作,最长的传输距离可以达到10米以上。为了确保信号在传输线当中传播时,不受反射信号的影响,LVDS信号要求传输线阻抗受控,其中单线阻抗为50ohms,差分阻抗100ohms。在实际应用当中,利用一些高速电路仿真分析工具,通过合理的设置层叠厚度和介质参数,调整走线的线宽和线间距,计算出单线和差分阻抗结果,来达到阻抗控制的目的。如下图,使用Mentor公司的ePlanner工具设计差分信号的布线规则,计算出单线和差分阻抗

例如通过如下的层叠和布线参数设计,得到单线阻抗为58.8Ω,差分阻抗为:102Ω

PCB层叠参数设置和阻抗计算结果

但是在很多时候,同时满足单线阻抗和差分阻抗是比较困难的。一方面,线宽(Width)和线间距(Separation)的调整范围会受到物理设计空间的限制,例如在BGA或直列型边缘连接器内的布线和线宽受焊盘尺寸和间距的限制;另一方面,W和S的改变都会影响到单线和差分阻抗的结果。因此,在一定的层叠条件下,了解W和S与阻抗之间的关系,对设计师设定差分布线规则就十分有意义了。利用Mentor公司的HyperLynx软件,可以很方便的计算出达到预定阻抗值的线宽和线间距关系。

这里的曲线表示在当前层叠和介质条件下,达到100ohms差分阻抗的线宽和线间距之间关系。通过这个曲线,我们可以迅速判断满足阻抗控制要求达到的物理规则。如果条件不能满足,则可以迅速改变层叠和介质参数,寻找新的结合点。

端接匹配(Termination)

LVDS信号的拓扑可以是点到点单向,点到点双向或总线型(multi-drop)。无论哪种应用,都需要在接收端进行端接匹配。匹配值一般等于差分组抗,为100ohms。匹配电阻在这里主要起到吸收负载反射信号的作用,因此要求放置的距离接收器端尽量靠近。很多器件将100 ohms匹配做到片内,在设计时可以选择使用片内的匹配电阻,从而简化设计和PCB layout工作。但是这个片内的匹配电阻,并不在用于仿真的IBIS模型中反映出来。因此在前仿真当中,需要添加这样一个匹配电阻;在后仿真时要使用what-if分析,在接收端使用虚拟匹配。否则,LVDS信号会因为没有终端匹配,产生差模干扰,影响仿真结果。

以下是使用Mentor公司的ePlanner仿真没有终端匹配和添加了终端匹配的LVDS信号波形。

1. ePlanner仿真点到点单向无匹配LVDS信号,信号频率为777MHz.

2. ePlanner仿真点到点单向匹配LVDS信号,信号频率为777MHz.

差分信号布线

一般来说,按照阻抗设计规则进行差分信号布线,就可以确保LVDS信号质量。在实际布线当中,LVDS差分信号布线应遵循以下几点:

1. 差分对应该尽可能地短、走直线、减少布线中的过孔数,差分对内的信号线间距必须保持一致;避免差分对布线太长,出现太多的拐弯。

2. 差分对与差分对之间应该保证10倍以上的差分对间距,减少线间串扰。必要时,在差分对之间放置隔离用的接地过孔。

3. LVDS差分信号信号不可以跨平面分割。尽管两根差分信号互为回流路径,跨分割不会割断信号的回流,但是跨分割部分的传输线会因为缺少参考平面而导致阻抗的不连续。

4. 尽量避免使用层间差分信号。在PCB板的实际加工过程中,由于层叠之间的层压对准精度大大低于同层蚀刻精度,以及层压过程中的介质流失,层间差分信号不能保证差分线之间间距等于介质厚度,因此会造成层间差分对的差分阻抗变化。因此建议尽量使用同层内的差分。

5. 在阻抗设计时,尽量设计成紧耦合方式(即差分对线间距小于或等于线宽),差分对与差分对之间。

关键词:LVDS,阻抗控制,端接匹配

LVDS(Low Voltage Differential Signal)低压差分信号,最早由美国国家半导体公司(National Semiconductor)提出的一种高速串行信号传输电平,由于它传输速度快,功耗低,抗干扰能力强,传输距离远,易于匹配等优点,迅速得到诸多芯片制造厂商和应用商的青睐,并通过TIA/EIA(Telecommunication Industry Association/Electronic Industries Association)的确认,成为该组织的标准(ANSI/TIA/EIA-644 standard)。LVDS信号被广泛应用于计算机、通信以及消费电子领域,并被以PCI-Express为代表的第三代I/O标准中采用。

传输线阻抗设计

LVDS信号的电压摆幅只有350MV, 为电流驱动的差分信号方式工作,最长的传输距离可以达到10米以上。为了确保信号在传输线当中传播时,不受反射信号的影响,LVDS信号要求传输线阻抗受控,其中单线阻抗为50ohms,差分阻抗100ohms。在实际应用当中,利用一些高速电路仿真分析工具,通过合理的设置层叠厚度和介质参数,调整走线的线宽和线间距,计算出单线和差分阻抗结果,来达到阻抗控制的目的。如下图,使用Mentor公司的ePlanner工具设计差分信号的布线规则,计算出单线和差分阻抗

例如通过如下的层叠和布线参数设计,得到单线阻抗为58.8Ω,差分阻抗为:102Ω

PCB层叠参数设置和阻抗计算结果

但是在很多时候,同时满足单线阻抗和差分阻抗是比较困难的。一方面,线宽(Width)和线间距(Separation)的调整范围会受到物理设计空间的限制,例如在BGA或直列型边缘连接器内的布线和线宽受焊盘尺寸和间距的限制;另一方面,W和S的改变都会影响到单线和差分阻抗的结果。因此,在一定的层叠条件下,了解W和S与阻抗之间的关系,对设计师设定差分布线规则就十分有意义了。利用Mentor公司的HyperLynx软件,可以很方便的计算出达到预定阻抗值的线宽和线间距关系。

这里的曲线表示在当前层叠和介质条件下,达到100ohms差分阻抗的线宽和线间距之间关系。通过这个曲线,我们可以迅速判断满足阻抗控制要求达到的物理规则。如果条件不能满足,则可以迅速改变层叠和介质参数,寻找新的结合点。

端接匹配(Termination)

LVDS信号的拓扑可以是点到点单向,点到点双向或总线型(multi-drop)。无论哪种应用,都需要在接收端进行端接匹配。匹配值一般等于差分组抗,为100ohms。匹配电阻在这里主要起到吸收负载反射信号的作用,因此要求放置的距离接收器端尽量靠近。很多器件将100 ohms匹配做到片内,在设计时可以选择使用片内的匹配电阻,从而简化设计和PCB layout工作。但是这个片内的匹配电阻,并不在用于仿真的IBIS模型中反映出来。因此在前仿真当中,需要添加这样一个匹配电阻;在后仿真时要使用what-if分析,在接收端使用虚拟匹配。否则,LVDS信号会因为没有终端匹配,产生差模干扰,影响仿真结果。

以下是使用Mentor公司的ePlanner仿真没有终端匹配和添加了终端匹配的LVDS信号波形。

1. ePlanner仿真点到点单向无匹配LVDS信号,信号频率为777MHz.

2. ePlanner仿真点到点单向匹配LVDS信号,信号频率为777MHz.

差分信号布线

一般来说,按照阻抗设计规则进行差分信号布线,就可以确保LVDS信号质量。在实际布线当中,LVDS差分信号布线应遵循以下几点:

1. 差分对应该尽可能地短、走直线、减少布线中的过孔数,差分对内的信号线间距必须保持一致;避免差分对布线太长,出现太多的拐弯。

2. 差分对与差分对之间应该保证10倍以上的差分对间距,减少线间串扰。必要时,在差分对之间放置隔离用的接地过孔。

3. LVDS差分信号信号不可以跨平面分割。尽管两根差分信号互为回流路径,跨分割不会割断信号的回流,但是跨分割部分的传输线会因为缺少参考平面而导致阻抗的不连续。

4. 尽量避免使用层间差分信号。在PCB板的实际加工过程中,由于层叠之间的层压对准精度大大低于同层蚀刻精度,以及层压过程中的介质流失,层间差分信号不能保证差分线之间间距等于介质厚度,因此会造成层间差分对的差分阻抗变化。因此建议尽量使用同层内的差分。

5. 在阻抗设计时,尽量设计成紧耦合方式(即差分对线间距小于或等于线宽),差分对与差分对之间。

引言:随着电子设计技术的不断进步,要求更高速率信号的互连。在传统并行同步数字信号的数位和速率将要达到极限的情况下,设计师转向从高速串行信号寻找出路。HyperTansport(by AMD), Infiniband(by Intel),PCI-Express(by Intel)等第三代I/O总线标准(3GI/O)不约而同地将低压差分信号(LVDS)作为下一代高速信号电平标准。本文将从LVDS信号仿真、设计,测试等多方面探讨合适的LVDS信号的实现。

关键词:LVDS,阻抗控制,端接匹配

LVDS(Low Voltage Differential Signal)低压差分信号,最早由美国国家半导体公司(National Semiconductor)提出的一种高速串行信号传输电平,由于它传输速度快,功耗低,抗干扰能力强,传输距离远,易于匹配等优点,迅速得到诸多芯片制造厂商和应用商的青睐,并通过TIA/EIA(Telecommunication Industry Association/Electronic Industries Association)的确认,成为该组织的标准(ANSI/TIA/EIA-644 standard)。LVDS信号被广泛应用于计算机、通信以及消费电子领域,并被以PCI-Express为代表的第三代I/O标准中采用。

传输线阻抗设计

LVDS信号的电压摆幅只有350MV, 为电流驱动的差分信号方式工作,最长的传输距离可以达到10米以上。为了确保信号在传输线当中传播时,不受反射信号的影响,LVDS信号要求传输线阻抗受控,其中单线阻抗为50ohms,差分阻抗100ohms。在实际应用当中,利用一些高速电路仿真分析工具,通过合理的设置层叠厚度和介质参数,调整走线的线宽和线间距,计算出单线和差分阻抗结果,来达到阻抗控制的目的。如下图,使用Mentor公司的ePlanner工具设计差分信号的布线规则,计算出单线和差分阻抗

例如通过如下的层叠和布线参数设计,得到单线阻抗为58.8Ω,差分阻抗为:102Ω

PCB层叠参数设置和阻抗计算结果

但是在很多时候,同时满足单线阻抗和差分阻抗是比较困难的。一方面,线宽(Width)和线间距(Separation)的调整范围会受到物理设计空间的限制,例如在BGA或直列型边缘连接器内的布线和线宽受焊盘尺寸和间距的限制;另一方面,W和S的改变都会影响到单线和差分阻抗的结果。因此,在一定的层叠条件下,了解W和S与阻抗之间的关系,对设计师设定差分布线规则就十分有意义了。利用Mentor公司的HyperLynx软件,可以很方便的计算出达到预定阻抗值的线宽和线间距关系。

这里的曲线表示在当前层叠和介质条件下,达到100ohms差分阻抗的线宽和线间距之间关系。通过这个曲线,我们可以迅速判断满足阻抗控制要求达到的物理规则。如果条件不能满足,则可以迅速改变层叠和介质参数,寻找新的结合点。

端接匹配(Termination)

LVDS信号的拓扑可以是点到点单向,点到点双向或总线型(multi-drop)。无论哪种应用,都需要在接收端进行端接匹配。匹配值一般等于差分组抗,为100ohms。匹配电阻在这里主要起到吸收负载反射信号的作用,因此要求放置的距离接收器端尽量靠近。很多器件将100 ohms匹配做到片内,在设计时可以选择使用片内的匹配电阻,从而简化设计和PCB layout工作。但是这个片内的匹配电阻,并不在用于仿真的IBIS模型中反映出来。因此在前仿真当中,需要添加这样一个匹配电阻;在后仿真时要使用what-if分析,在接收端使用虚拟匹配。否则,LVDS信号会因为没有终端匹配,产生差模干扰,影响仿真结果。

以下是使用Mentor公司的ePlanner仿真没有终端匹配和添加了终端匹配的LVDS信号波形。

1. ePlanner仿真点到点单向无匹配LVDS信号,信号频率为777MHz.

2. ePlanner仿真点到点单向匹配LVDS信号,信号频率为777MHz.

差分信号布线

一般来说,按照阻抗设计规则进行差分信号布线,就可以确保LVDS信号质量。在实际布线当中,LVDS差分信号布线应遵循以下几点:

1. 差分对应该尽可能地短、走直线、减少布线中的过孔数,差分对内的信号线间距必须保持一致;避免差分对布线太长,出现太多的拐弯。

2. 差分对与差分对之间应该保证10倍以上的差分对间距,减少线间串扰。必要时,在差分对之间放置隔离用的接地过孔。

3. LVDS差分信号信号不可以跨平面分割。尽管两根差分信号互为回流路径,跨分割不会割断信号的回流,但是跨分割部分的传输线会因为缺少参考平面而导致阻抗的不连续。

4. 尽量避免使用层间差分信号。在PCB板的实际加工过程中,由于层叠之间的层压对准精度大大低于同层蚀刻精度,以及层压过程中的介质流失,层间差分信号不能保证差分线之间间距等于介质厚度,因此会造成层间差分对的差分阻抗变化。因此建议尽量使用同层内的差分。

5. 在阻抗设计时,尽量设计成紧耦合方式(即差分对线间距小于或等于线宽),差分对与差分对之间。

关键词:LVDS,阻抗控制,端接匹配

LVDS(Low Voltage Differential Signal)低压差分信号,最早由美国国家半导体公司(National Semiconductor)提出的一种高速串行信号传输电平,由于它传输速度快,功耗低,抗干扰能力强,传输距离远,易于匹配等优点,迅速得到诸多芯片制造厂商和应用商的青睐,并通过TIA/EIA(Telecommunication Industry Association/Electronic Industries Association)的确认,成为该组织的标准(ANSI/TIA/EIA-644 standard)。LVDS信号被广泛应用于计算机、通信以及消费电子领域,并被以PCI-Express为代表的第三代I/O标准中采用。

传输线阻抗设计

LVDS信号的电压摆幅只有350MV, 为电流驱动的差分信号方式工作,最长的传输距离可以达到10米以上。为了确保信号在传输线当中传播时,不受反射信号的影响,LVDS信号要求传输线阻抗受控,其中单线阻抗为50ohms,差分阻抗100ohms。在实际应用当中,利用一些高速电路仿真分析工具,通过合理的设置层叠厚度和介质参数,调整走线的线宽和线间距,计算出单线和差分阻抗结果,来达到阻抗控制的目的。如下图,使用Mentor公司的ePlanner工具设计差分信号的布线规则,计算出单线和差分阻抗

例如通过如下的层叠和布线参数设计,得到单线阻抗为58.8Ω,差分阻抗为:102Ω

PCB层叠参数设置和阻抗计算结果

但是在很多时候,同时满足单线阻抗和差分阻抗是比较困难的。一方面,线宽(Width)和线间距(Separation)的调整范围会受到物理设计空间的限制,例如在BGA或直列型边缘连接器内的布线和线宽受焊盘尺寸和间距的限制;另一方面,W和S的改变都会影响到单线和差分阻抗的结果。因此,在一定的层叠条件下,了解W和S与阻抗之间的关系,对设计师设定差分布线规则就十分有意义了。利用Mentor公司的HyperLynx软件,可以很方便的计算出达到预定阻抗值的线宽和线间距关系。

这里的曲线表示在当前层叠和介质条件下,达到100ohms差分阻抗的线宽和线间距之间关系。通过这个曲线,我们可以迅速判断满足阻抗控制要求达到的物理规则。如果条件不能满足,则可以迅速改变层叠和介质参数,寻找新的结合点。

端接匹配(Termination)

LVDS信号的拓扑可以是点到点单向,点到点双向或总线型(multi-drop)。无论哪种应用,都需要在接收端进行端接匹配。匹配值一般等于差分组抗,为100ohms。匹配电阻在这里主要起到吸收负载反射信号的作用,因此要求放置的距离接收器端尽量靠近。很多器件将100 ohms匹配做到片内,在设计时可以选择使用片内的匹配电阻,从而简化设计和PCB layout工作。但是这个片内的匹配电阻,并不在用于仿真的IBIS模型中反映出来。因此在前仿真当中,需要添加这样一个匹配电阻;在后仿真时要使用what-if分析,在接收端使用虚拟匹配。否则,LVDS信号会因为没有终端匹配,产生差模干扰,影响仿真结果。

以下是使用Mentor公司的ePlanner仿真没有终端匹配和添加了终端匹配的LVDS信号波形。

1. ePlanner仿真点到点单向无匹配LVDS信号,信号频率为777MHz.

2. ePlanner仿真点到点单向匹配LVDS信号,信号频率为777MHz.

差分信号布线

一般来说,按照阻抗设计规则进行差分信号布线,就可以确保LVDS信号质量。在实际布线当中,LVDS差分信号布线应遵循以下几点:

1. 差分对应该尽可能地短、走直线、减少布线中的过孔数,差分对内的信号线间距必须保持一致;避免差分对布线太长,出现太多的拐弯。

2. 差分对与差分对之间应该保证10倍以上的差分对间距,减少线间串扰。必要时,在差分对之间放置隔离用的接地过孔。

3. LVDS差分信号信号不可以跨平面分割。尽管两根差分信号互为回流路径,跨分割不会割断信号的回流,但是跨分割部分的传输线会因为缺少参考平面而导致阻抗的不连续。

4. 尽量避免使用层间差分信号。在PCB板的实际加工过程中,由于层叠之间的层压对准精度大大低于同层蚀刻精度,以及层压过程中的介质流失,层间差分信号不能保证差分线之间间距等于介质厚度,因此会造成层间差分对的差分阻抗变化。因此建议尽量使用同层内的差分。

5. 在阻抗设计时,尽量设计成紧耦合方式(即差分对线间距小于或等于线宽),差分对与差分对之间。

评论