数字和取样示波器的关键器件和电路(05-100)

数字示波器的关键器件

本文引用地址://m.amcfsurvey.com/article/91573.htm数字存储示波器的关键器件——输入前端模/数转变器,通常是测量仪器公司自行设计和专用的高速集成电路,不供市售,例如TeK公司用在TDS5000等系列使用的带宽500MHz以上的ADC,由TeK和IBM共同开发制造,成本很高,只供维修时更换。直到今年Atmel公司推出AT84AS系列高速ADC,才有带宽1GHz,取样率2GS/S,分辨率10位的产品可供使用。现在,电子应用工程师可购买到高速高精度的ADC,构建数据采集系统、数字存储示波器、自动测试系统、直接射频转换器等高频电路。Atmel供应的AT84AS系列,目前有两个型号:AT84AS003和AT84AS004,前者的取样率1.5GS/S,后者的取样率2GS/S,两者完全兼容,AT84AS004的主要特征为:

·最高取样率-2GS/S

·最高分辨率-10位

·模拟输入电压和阻抗-500mv,100Ω(差分)、50Ω(单端);

·模拟输入带宽-3.3GHz

·1GHz的高频特性—有效位数7.8位,信噪比51dB,无杂波动态范围-55dB,

·调节功能-ADC增益,取样延迟,数据有效输出,超量程指示输出,1:4多工信号输出。

·供电电压—-5V,-2.2V,3.3V,2.5Vp,功率耗散6.5W

·装封—-EBGA317,25×35mm

·工作温度-0℃~90℃(民用级)-20℃~110℃(工业级)

AT84AS004芯片的结构框图如图1所示,从图1可见,输入信号Vin经取样保持电路S/H,送入量化器和逻辑电路,在时钟输入CLR,取样延迟调节SDA、图形发生器有效位PGEB、复位脉冲DRRB作用下实现A/D转换过程。获得的A/D数据输出经解多路复用器DMUX和低压差分缓冲级LVDS放大,形成4路输出端口A、B、C、D,4组输出的10位数字信号供存储器、DSP等作数据处理使用。芯片的调节信号还有内建自测试BIST,异步复位ASYNRST,增益调节GA,二进制和灰度码选择B/GB,休眠状态SLEEP等。

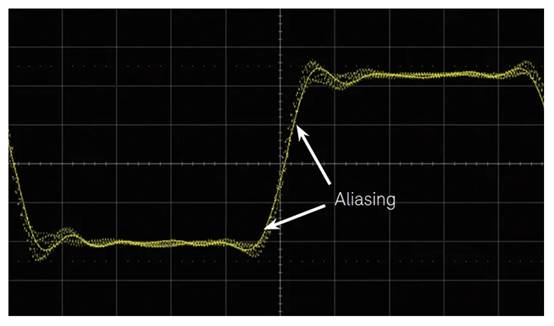

AT84S004芯片是目前市售频率指标最高的ADC。首先是取样率达到2GS/S,模拟输入带宽是3.3GHz。按取样原理可知,ΔF≤Fs/2即实时带宽应小于/等于取样率Fs。该芯片的Fs=2GS/s,求得△F=1GHz,即第一奈奎斯特区处在1GHz以下,第二奈奎斯特区扩展到2GHz。为避免产生波形混淆,数字存储示波器只使用第一奈奎斯特区,但是,双频通信应用时,可进入到第二奈奎斯特区,因为需为更宽的输入带宽。其次,在1GHz下的有效位数是7.8位而不是10位,由于时钟频率提高和电压比较器电平不稳,高频的分辨率会下降,从10位变成7.8位。大部分市售数字存储示波器的分辨率是8位。在高频时会低于7位。还有,芯片提供1:2和1:4的多工数字输出,对于后端数据处理非常有利,可以使用时钟较低的闪存和DSP,降低电路成本。

Atmel公司的AT84AS系列TDC仍在发展中,CMOS芯片的时钟频率可达到5GHz,表明该系列的取样率还有提高的潜力,Atmel今年已连续推出1.5GS/S和2GS/S两种ADC。Maxim公司的MAX108是8位分辨率和1.5GS/S的ADC,同样适用于数字存储示波器。

取样示波器的关键器体

取样示波器的关键器件是取样头,在原理上并非数/模转换过程而是开关过程。如果开关脉冲宽度用τ表示,等效带宽用ΔF表示,则求得ΔF=a1/τ,式中α是与开关脉冲波形有关的常数。例如,当τ=0时,ΔF =∞,亦即,开关脉冲宽度趋于零时,等效带宽趋于无限大。一般假设开关脉冲是钟形函数,此时,作为估算可取ΔF =0.35/τ,当τ=3.5ps,求得ΔF=100 GHz。

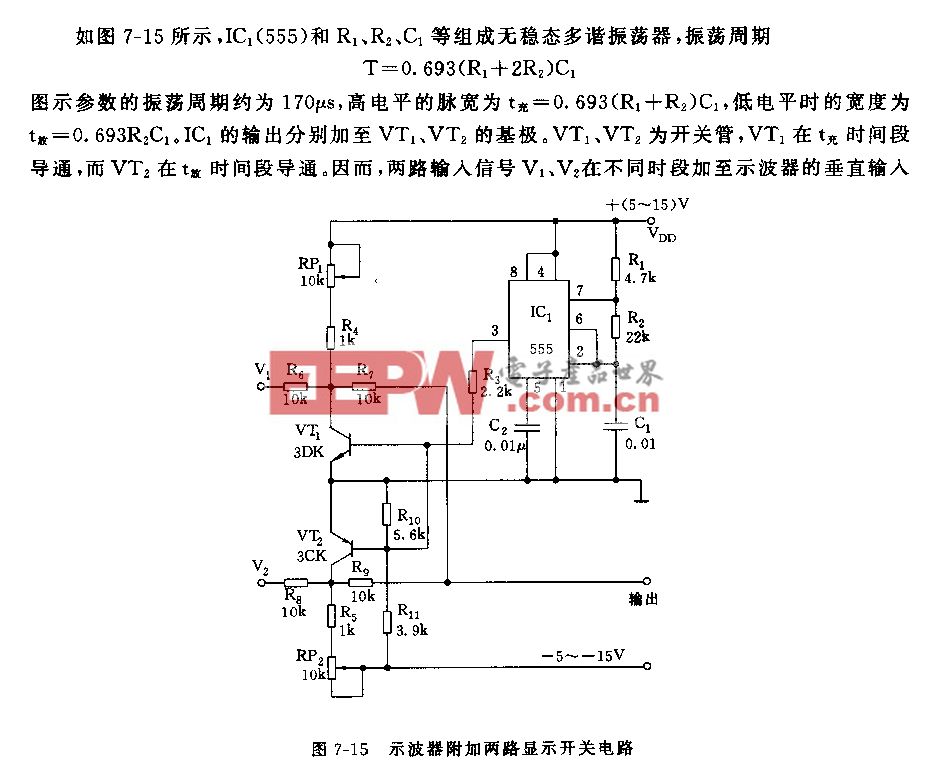

取样门电路可用桥式电路,通常采用如图2所示的双管半桥式开关电路。当输入的+LO和-LO驱动脉冲加到反向偏置的快速开关二极管对,+L0和-L0驱动脉冲分别由2PS微带线短路,产生1PS级的开关脉冲,并且对被测信号RF取样。取样获得的信号样品瞬间电荷保持在Chold电容对上,将取样电荷作处理和在慢速时间上对样品重建,即完成顺序取样的显示过程。由此可见,取样示波器在取样门实现高频高速的开关变换后,后端的信号处理可在低频低速下重建。如果后端采用数字处理,就是取样数字示波器,采用模拟处理,就是(模拟)取样示波器。

评论