利用频域时钟抖动分析加快设计验证过程(07-100)

——

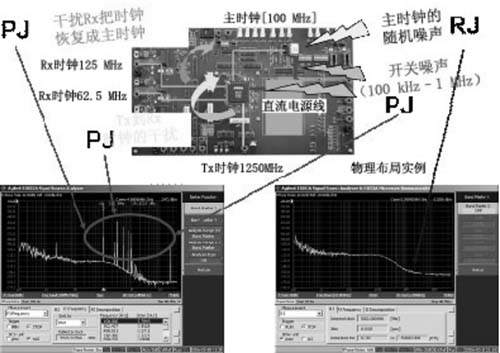

图4 实际环境中的抖动源

全面分析时钟信号要求达到飞秒级精度,只有相位噪声测量技术才能达到这种精度。相位噪声分析提供两种主要测量:S?(f?)和?(t),它们根据相位噪声测量带宽限制收集时钟的所有相位信息。

在相位噪声分析仪上分析RJ可以完成两个重要目标。首先,通过集成RJ频谱,可以提取预定带宽中的相应RJ高斯分布宽度。其次,通过分析S?(f?)的幂级数行为确定RJ的主要原因(图5)。

在相位噪声频谱中可以看到PJ分量的杂散。所以PJ频率知识对于诊断问题非常有帮助。参考每个PJ频率的PJ rms也能帮您了解每个PJ分量对总体时钟抖动的影响,查看去除主要PJ分量之后总体抖动的变化(图6)。

图5 分析相位噪声测量的RJ

评论