基于Xtensa的ASIP开发流程研究

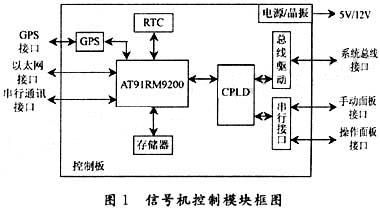

现在设计可编程处理器,很少是全新定制指令,普遍采用的方式是在已有的某RISC指令集基础上进行部分定制(或说扩展/自定义/优化指令)。理论上,为了研发一款ASIP式处理器,需要在已有GPP、ASIP、ASIC的基础上调整数据通路(Datapath),即增加功能单元,如图1所示的5级Pipeline处理器中添加自定义功能单元(Custom Unit),同时需要专用指令将操作数调入此自定义单元进行数据处理。为了实现指令扩展,首先需要分析应用目标数据处理算法的特性,从中找出那些经常出现且可以绑定的基本操作包;然后从众多实现方式(或大设计空间)如:(1)FLIX(VLIW或Multi-slot);(2)Vector(SIMD);(3)FUSED(Add-with-Shift-by-1)中选择最合适的途径[9-10]。因为设计者很难一次性找到最优途径,常常需要不同方式之间进行比较,因此一般需要某些EDA工具帮助快速实现指令自定义以及分析当前自定义指令对ASIP性能的影响。图2采用Top-down方式示意出ASIP设计的理论步骤。

本文引用地址://m.amcfsurvey.com/article/95269.htm

Xtensa开发工具集

目前,可用于ASIP体系结构及指令系统开发的EDA工具,包括Tensilica的Xtensa开发工具集(Xplorer、XCC、XPRES、XTMS、XEnergy),CoWare的Processor Design,University of Campinas的ArchC等。但Tensilica 的Xtensa开发工具集因功能强大而得到广泛应用。

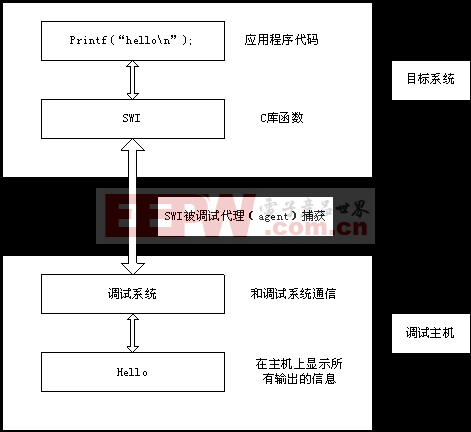

Tensilica针对SoC应用而设计的Xtensa系列可配置处理器及其开发工具,提供了一种自动化程度非常高的开发流程,该流程包括仿真C/SystemC级算法、调整处理器体系结构、向基本处理器添加专用指令、自动生成硬件RTL代码和与之相匹配的软件工具链(如编译器等),通过可配置处理器技术和TIE(Tensilica Instruction Extension)指令扩展技术替代了RTL开发。和ASIP相关的具体功能如下。

评论