微捷码宣布推出65纳米低功耗工艺的参考流程

芯片设计解决方案供应商微捷码(Magma®)设计自动化有限公司日前宣布,一款支持新加坡特许半导体制造公司新一代增强的65纳米低功耗工艺的基于Common Platform技术、基于Talus®的低功耗RTL-to-GDSII集成电路(IC)设计流程正式面市。这项增强的65纳米低功耗工艺被简称为65nm LPe;它通过利用创新性减少漏电技术,可显著降低高达50%的片上系统(SoC)待机功耗。

本文引用地址://m.amcfsurvey.com/article/96612.htm基于微捷码TalusIC实现系统,这款支持Chartered 65LPe的低功耗参考流程包含进了TalusPower Pro,通过在单一环境中贯穿整个实现阶段地使用各种技术,从而将功耗降至最低,同时最大程度提高性能并缩短设计周期。

这款参考流程完全支持统一功率格式(UPF),通过使用有低功耗设计意向的规则和Chartered 65nm LPe工艺,可用以实现包含有ARM(R)标准单元和存储器知识产权(IP)以及Aragio解决方案I/O库的复杂层次化设计。作为广大EDA供应商都支持的一项标准,统一功率格式(UPF)可支持所有适用于低功耗设计的设计流程和解决方案。

“当我们的客户想要低功耗解决方案时,他们也想要可帮助他们以更少风险、更快速度上市的解决方案。通过与微捷码等合作伙伴的密切合作,我们能够提供可帮助设计团队达成其项目目标的集成化低功耗解决方案,” Chartered公司实现联盟副总裁Walter Ng.表示。“通过实现复杂的层次化设计,微捷码Talus实现系统证明其最大程度提高我们增强的65纳米低功耗工艺优势的能力。”

“功耗一直以来都是便携式和消费类设备的一个头疼问题,不过现在却成为了横跨多个应用部分的一个驱动需求,”微捷码设计实施业务部总经理Premal Buch表示。“我们很高兴能为Chartered 65nm LPe工艺参考流程提供支持、能帮助加速结合低功耗技术的下一代芯片的开发。”

Talus低功耗设计实现流程

微捷码通用平台(Common Platform)的65纳米低功耗参考流程以包括Talus Design和Talus Vortex在内的Talus实现系统为基础,为高性能、高复杂度、低功耗纳米设计提供了一个完全集成化的RTL-to-GDSII流程。

Talus Power Pro通过与全芯片综合环境Talus Design和Talus Vortex物理设计解决方案结合使用,可贯穿整个流程地实现最佳功率管理。它提供了有功耗意识的综合、物理优化、时钟树综合和布线等功能,使得设计师能够最大程度降低功耗,确保一致的功率分布。

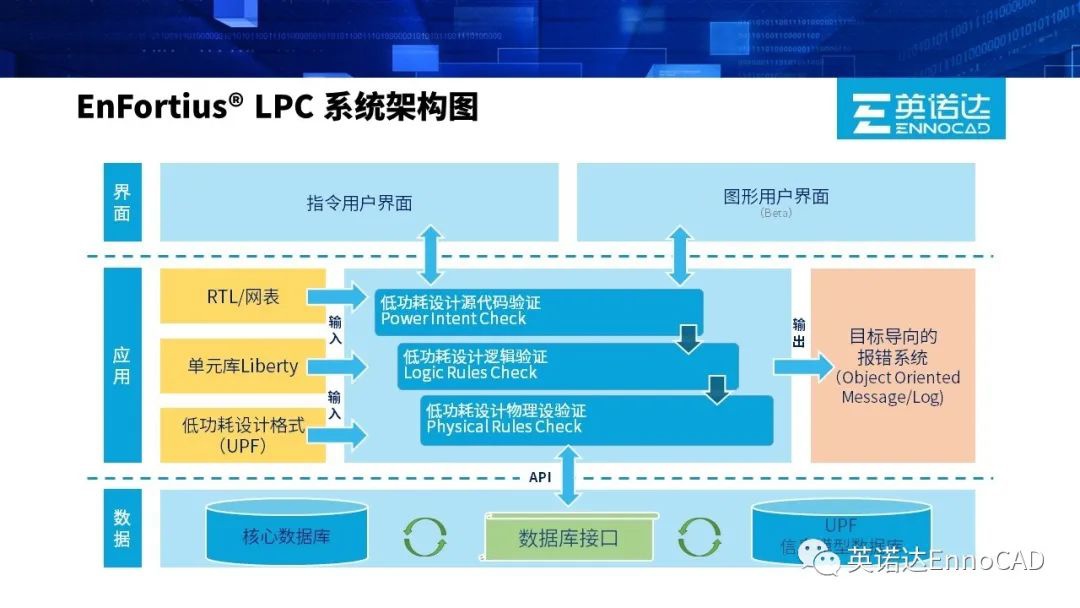

Talus Power Pro可在RTL-to-GDSII流程初期从UPF文件中读入功率约束。时钟门控、保持触发器综合(retention-flop synthesis)和多电压域(multi-Vdd)定义等功率约束可被定义以实现动态功耗降低;保持单元等特殊单元在综合阶段可以为支持多电压域流程推断生成;对于电源关闭的区域,电源开关在寄存器转换层(RTL)阶段可以被推断生成,便于仿真;状态表可用以定义已建立的不同电源域间的关系。此外,Talus Power Pro还可在设计流程的任何时候写出UPF文件,实现与第三方工具的简单互操作性。

Talus Design可被用于RTL快速开发和贯穿整个设计工艺的芯片级约束、自动化数据路径综合并平面布局原型的生成;Talus Vortex是一款完整的物理实现系统,提供了较常规单点工具流程更为卓越的时序和信号完整性、更小的面积、更低的功耗、更好的可制造性、更快的周期时间和更高的容量。

面市时间

这款参考流程现已可供微捷码客户免费使用。您可发送电子邮件到微捷码的代工厂支持团队FoundrySupport@magma-da.com或联系微捷码销售代表进行申请获得。

评论