用CPLD制作高速频率计

该频率计测量的范围为1Hz~999MHz,分4挡,测量精度分别为1、10、100、1000Hz.全部逻辑电路由一片CPLD实现.外部只需安装6位LED数码管、4位互锁开关、有源晶振、输人信号整形的施密特触发器和电源便可.CPLD的内部逻辑用VHDL+原理图混合设计的方法实现,设计完成后,再经功能仿真和时序仿真,即可综合生成下载文件,下载到器件中运行.

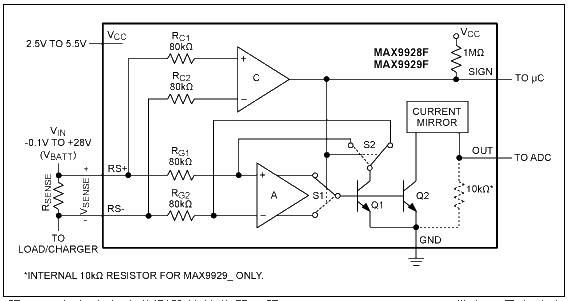

频率计的原理框图如图1所示.用低速精准的参考频率作计数器的选通信号.

在参考频率的周期内对被测频率计数.其计数值和参考频率的比值即为被测频率值.由于计数器的工作频率和系统时钟无关,所以,在很低的系统时钟频率下就可以测量很高的频率,最高测量频率仅受限于计数器的最大计数频率.调整参考频率,可获得不同的测量范围和精度.

根据选择的测量挡,参考

频率分别为1、10、100、1000Hz,这样,计数器的值即为被测频率的整数或小数倍.若使用十进制计数器.将计数器的值直接输出到数码管.并设置好相应的小数点位置,数码管所显示的数值即为实际频率值.

频率计的面板如图2所示.其中Gate为门控信号输出指示;若计数器溢出,则Over指示灯亮,表示超量程.

频率计的顶屡电路图如图3所示.

S1-S1000为挡位选择输入端,互锁,低电平有效;clk为1MHz系统时钟;FM为被测频率输人端;测量结果由dop、a-g端送数码管显示;动态扫描信号由q[5..0]端轮流产生,低电平有效;gate、over.端分别从引脚输出,低有效.

CPLD实现了顶层原理图的所有逻辑功能.各子块的大部分采用VHDL描述完成.系统时钟经fidiv模块分频后,产生1、10、100、1000Hz四个基准频率,由sel_freq模块根据当前选择的挡位选择一路送往control模块.产生门控、计数器复位、锁存器锁存三路信号,其时序如图4所示.门控信号GATE为参考频率的二分频,在ga的高电平期间,十进制计数器进行计数.低电平则停止计数,随后产生锁存信号,更新锁存的计数值,然后延时一段时间.将计数器复位,准备下一周期的计数.六位十进制计数器的计数值经锁存后送数码管显示.

SCAN子系统的原理图如图5所示,各个模块由VHDL描述实现.由fidlv分频所得的1000Hz的脉冲送人scan的clkin端,作为六路数码管扫描时钟.

LEDSEL模块进行0~5的循环计数,其计数值N除作为点亮第N+1个数码管的扫描选通信号外,还应送到各个模块,通知当前显示的是哪一位.Mux多路开关根据计数值选通一路锁存器,送显示译码器译码输出.

dot模块根据计数值和当前的挡位,送出点亮小数点的信号.hide的作用是熄灭数值前面多余的0,如显示为0001.2,则bide在扫描煎3个0时,送出灭0信号到译码器,禁止译码,其灭0信号由扫描计数值、当前挡位和锁存输出来决定.

本频率计已在ALTEra公司MAX7000系列的EPM7128SLC和LattICe公司的M4A5-128/64-10YC两种型号的CPLD上实现.

这两种CPLD都含有128个宏单元,对本设计来说利用率较高.若采用Altera的器件进行设计,建议使用Altem的QUARTusⅡ4.0进行综合.最好不要选择Max+plusⅡ进行综合,因为Max+plusⅡ对VHDL的综合能力和器件的适配能力都较QuartusⅡ差,使用Max+plusⅡ可能出现器件资源不足的错误.另外在业余条件下最好使用EPM7128SLC,因为器件封装(PI+CC-84PINs)、电压(5V)、编程(支持JTAG ISP)都比较适宜.

评论