一种基于FPGA的高速误码测试仪的设计

方案描述:误码测试仪是检测通信系统可靠性的重要设备。传统的误码测试仪,基于CPLD和CPU协同工作,不仅结构复杂,价格昂贵,而且不方便携带。基于FPGA的告诉误码测试仪,采用FPGA来完成控制和测试模块的一体化设计,提高了系统功能扩展性和系统的集成度,使得各个功能模块在不改动硬件电路的情况下可以相应变化。在发送端发送M序列作为测试数据,其测试速度最高可达到155MB/S。由于将其物理层上的各种协议层得功能集中到FPGA内部实现,减少了硬件和软件的复杂度,并且缩短了系统的开发周期,具有可生气的特点。

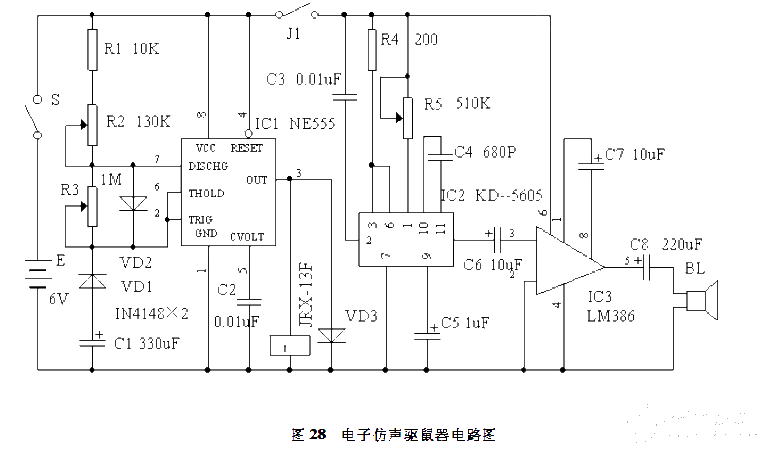

方案设计图

![20120109_1051395139_[32]_FPGA误码测试仪_plan.png 20120109_1051395139_[32]_FPGA误码测试仪_plan.png](http://m.amcfsurvey.com/uphotos/1415927710/pics/99f083cbd26c2d1c0277b1b4b0634153.png)

方案关键器件表

|

类型

|

型号

|

厂商

|

说明

|

|---|---|---|---|

|

FPGA

|

XC6VCX75T-1FFG784

|

Xilinx

|

误码测试仪应用 |

评论

了解学习一下。

学习