超低功耗嵌入式系统设计技巧

2 降低系统功耗的途径

①降低集成电路的动态功耗。根据式(1)可知,要降低集成电路的动态功耗,途径有:a.降低活动因子,也就是降低电容充放电的平均次数。b.降低电源电压。因为动态功耗与电压的平方成正比,瞬时导通功耗与电压成正比,因此在满足电路速度的前提之下,降低电源电压是降低电路功耗的最有效的办法。c.降低负载电容。为了减小负载电容,在工艺方面可以选择小的器件,物理实现时减小连线的长度。d.降低开关频率,在式(1)中,电路的功耗与工作频率成正比,因此降低时钟频率可以直接降低动态功耗。

②尽可能选用静态功耗小的CMOS集成芯片,以降低系统的静态漏电功耗。

③尽可能地减少纯电阻的使用。纯电阻是耗能元件,电能直接转化为热能消耗掉了,所以要尽可能地避免电阻的使用。

④减少有源开关器件的使用。有源开关器件(如晶体管)在状态转换期间有比较大的电流消耗,减少这类器件的使用有助于减小功耗。本文引用地址://m.amcfsurvey.com/article/151493.htm

3 设计技巧

3.1 硬件方面

在器件选择上,要尽量实现全CMOS化的硬件设计。在设计超低功耗系统时,要对电源电压、时钟频率以及静态功耗进行控制,并遵循系统硬件设计的4项基本原则:电压能低就不高,频率能慢就不快,系统能静(态)就不动(态),电源能断就不通。

3.1.1 微处理器选择

随着低功耗系统需求的增加,很多单片机厂商都推出了自己的低功耗产品,如Philips公司的P8XLPC系列,TI公司的MSP430系列,Micro-chip公司的PIC单片机以及NXP公司的ARM Cortex-M0系列。如果处理器本身具有超低功耗特性,首先必须能在低电压和低频率工作,其次还要看单片机自身的特性,看是否是面向超低功耗应用而设计的单片机,需要对处理器的工作模式、工作电流、休眠电流、掉电电流作详细的统计。

Microchip公司采用nanoWatt XLP(eXtreme Low Power)极低功耗技术的MCU的典型电流消耗为:掉电电流小于100 nA;看门狗电流消耗小于800 nA;实时时钟和日历电流消耗小于800 nA。该公司的PIC24F16KA系列的MCU,典型休眠电流可以低至20 nA,实时时钟电流490 nA,看门狗定时器电流370 nA。该系列的MCU可使应用连续运行20年以上而无需更换电池。

NXP公司采用ARM Cortex-M0内核的LPCllxx系列32位处理器的能耗仅为85μW/MHz,此系列处理器的功耗统计如表1和表2所列。

3.1.2 外围集成电路

与TTL数字集成电路相比,CMOS数字集成电路在低功耗特性上具有无可比拟的优越性能。在存储容量需求较小的条件下,采用FRAM代替一般的Flash或E2PROM,将会节省很多电能,因为FRAM的写入功耗是Flash和E2PROM的1/1 000~1/100 000。

3.1.3 低电压供电

目前许多芯片的电源电压范围都比较宽,系统的功耗和系统的供电电压存在着一定的函数关系。对于纯电阻电路,功耗为P=V2/R;对于容性负载电路,动态功耗为,见式(1)。从以上2式可以看出,系统的功耗与系统供电电压的平方成正比。当供电电压由5 V降到3.3 V时,功耗将减少50%以上;当电压降到1.8 V时,功耗将减少80%以上,如图3所示。

3.1.4 分区供电

分区供电就是要控制电源供电部分,需要对电源进行分割,使系统功能模块的电源供电相对独立,同时实现其可控设计,便于独立供电和动态管理;在闲置时利用开关控制各个部分的关断,以节省电能。在系统休眠或掉电工作时关掉外围电路的电源,仅仅保留CPU和定时器电路的电源。分区控制电源电路示意图如图4所示。

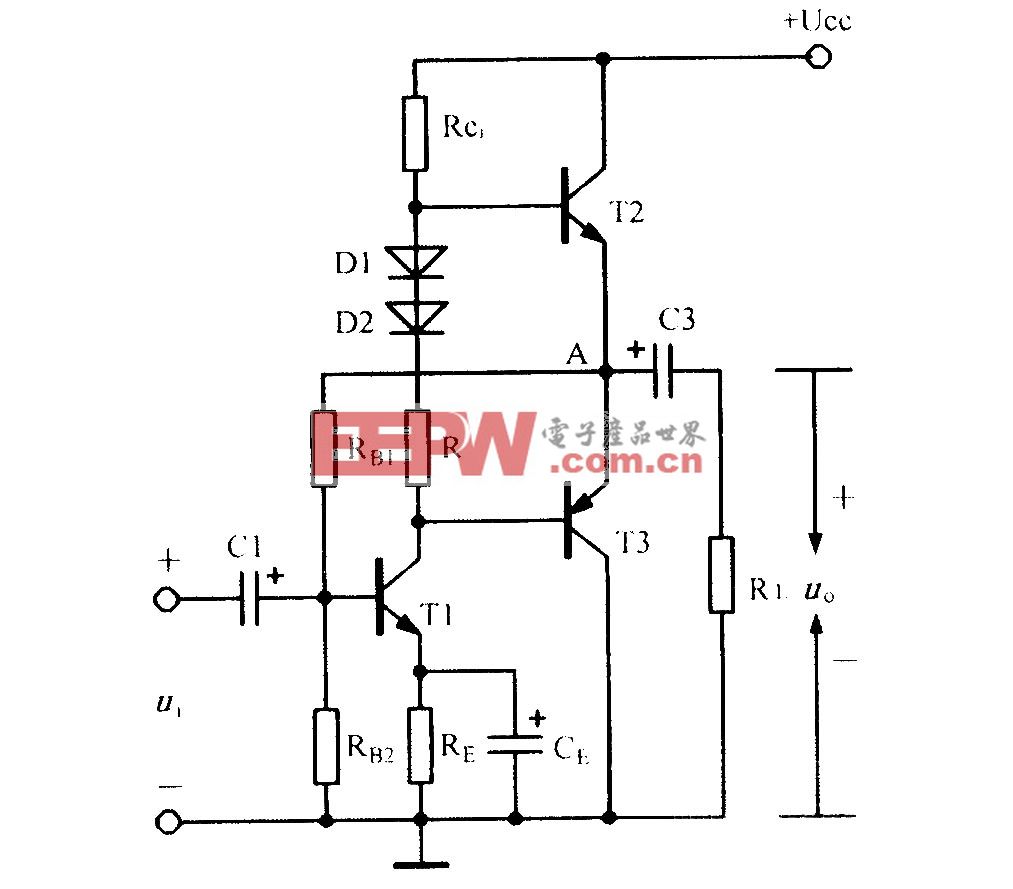

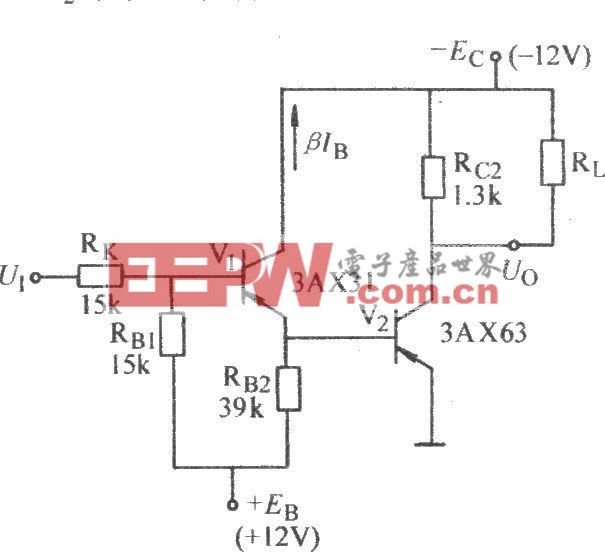

图4中的晶体管用作电源开关,控制电源VCC向分区供电部分供电,供电控制端接到处理器的输出引脚上。对于图4(a)中的PNP管,高电平切断分区供电部分的电源,低电平使PNP晶体管导通,此时VCC向分区供电部分供电;对于图4(b)中的NPN管,供电情形则相反。

评论