多片DDC芯片HSP50214B与DSP接口电路设计

多片DDC的同步还需要内部工作时钟的同步,这是通过主从配置实现的,芯片的前端工作电路由输入时钟(CLKIN)实现同步,而后端电路由工作时钟(PROCLK)实现同步, 为了使四片DDC和EPLD之间系统时钟同步,系统要求用一个时钟信号源产生四路相干时钟分别分配给EPLD和四片HSP50214B,这给保证时钟信号的驱动能力和信号完整性带来了难度。系统的解决办法是将温补晶振产生的40MHz时钟信号首先传送到一个零延迟时钟驱动芯片CY2305的输入端,再由该芯片输出五路同步时钟信号,其中一路时钟直接供给EPLD,其它四路时钟分别输入HSP50214B的输入时钟CLKIN和工作时钟PROCLK。

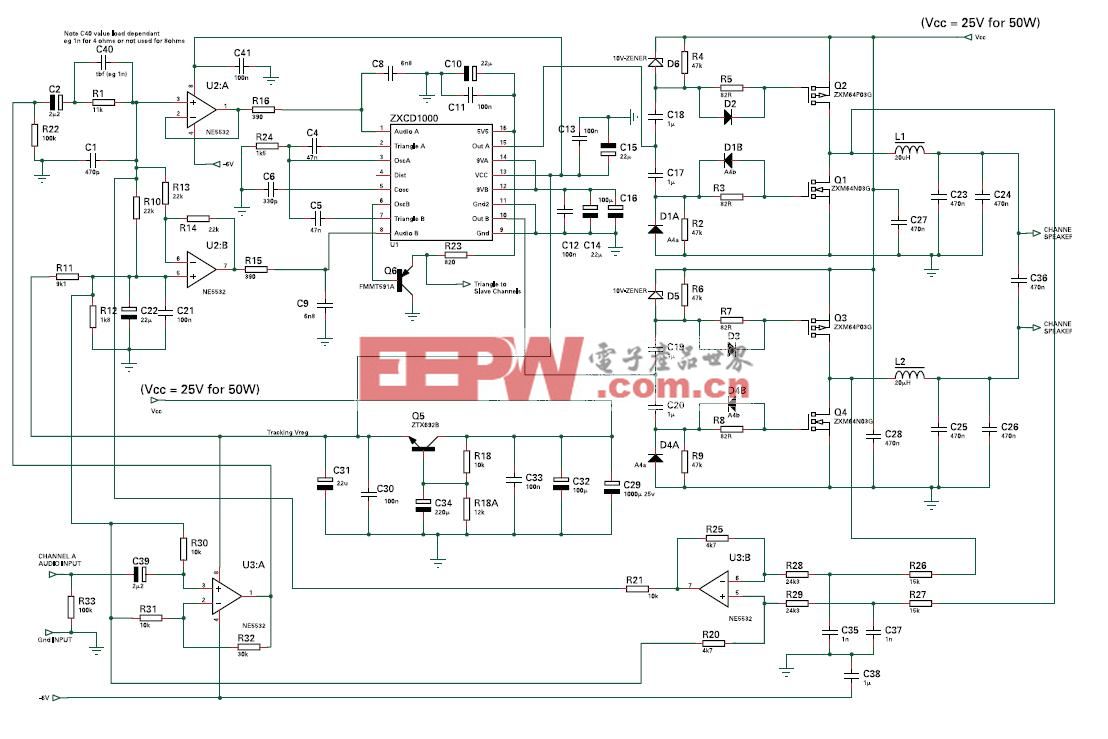

DDC之间由SYNCOUT,SYNCIN1,SYNCIN2,MSYNCO和MSYNCI来控制同步时序, 如图2所示。MSYNCO是多芯片同步输出引脚,系统中HSP50214B_1配置为主芯片,它的MSYNCO输出连接至四片HSP50214B的MSYNIN引脚;SYNCOUT引脚由前端时钟CLKIN或工作时钟PROCLK产生,用以同步芯片内部工作,其中HSP50214B_1的SYNCOUT引脚连接至四片HSP50214B芯片的SYNCIN2引脚,用以同步DDC芯片内部的FIR滤波以及自动控制增益(AGC)部分;HSP50214B_2的SYNCOUT引脚连接至四片HSP50214B芯片的SYNCIN1引脚,用以同步DDC芯片内部的CIC抽取滤波以及数控振荡器部分。

结 语

在“基于电视信号的无源雷达信号处理”项目中,笔者设计的中频采集板卡对接收机输出的4路伴音和图像中频信号进行高速采集与数字下变频。笔者在电路设计中采用了本文提出的DSP控制多片DDC芯片的接口设计方案,对于4路A/D转换后的高速信号,分别通过DDC进行下变频和多级抽取滤波。该无源雷达信号处理机已经通过了外场试验验证,其中的中频采集板卡经测试可以精确实现数字下变频功能,精确度为0.01Hz;抽取模块实现信号速率400倍降低;滤波环节有效地增大了采集卡的动态范围31dB,很好地满足了无源雷达信号处理机的指标要求。

评论