基于SOPC的EDSL Modem的研制

3硬件平台的设计

EDSLModem硬件平台的搭建主要使用了 Altera公司的 FPGA Cyclone EP1C6Q240C8芯片,它拥有充足的可编程逻辑资源内嵌32位Nios-II软核处理器来实现整个可编程嵌入式系统。系统的主要功能由FPGA实现,硬件电路除 FPGA外只需加上存储器件、以太网控制芯片和前端AD/DA转换芯片即可。本系统主要使用了一片 8M Byte Flash,一片16M Byte SDRAM,以及以太网接口控制芯片等作为FPGA的外围设备,硬件结构简单明了,极大提高了系统的可靠性。FPGA系统运行时钟为50MHz,充分保证了系统的运行速度。

在硬件平台的搭建中主要用到了Altera公司的Quartus-II与SOPCBuilder软件,其中 Quartus-II能进行系统及各逻辑部件的设计输入、编译、仿真、综合、布局布线,并进行位流文件的下载和配置文件的烧录,以及使用片内逻辑分析仪进行分析和验证。SOPCBuilder嵌入在Quartus-II开发系统内,是一个自动系统开发工具,能够自动进行系统定义,完成SOPC开发的集成过程。在SOPC Builder 中选取系统所需部件,并自动生成每个部件的系统级HDL 文件以及支持部件所需的软件,如驱动程序、库文件和一些实用的应用程序等,以供软件开发 原型用[4]。

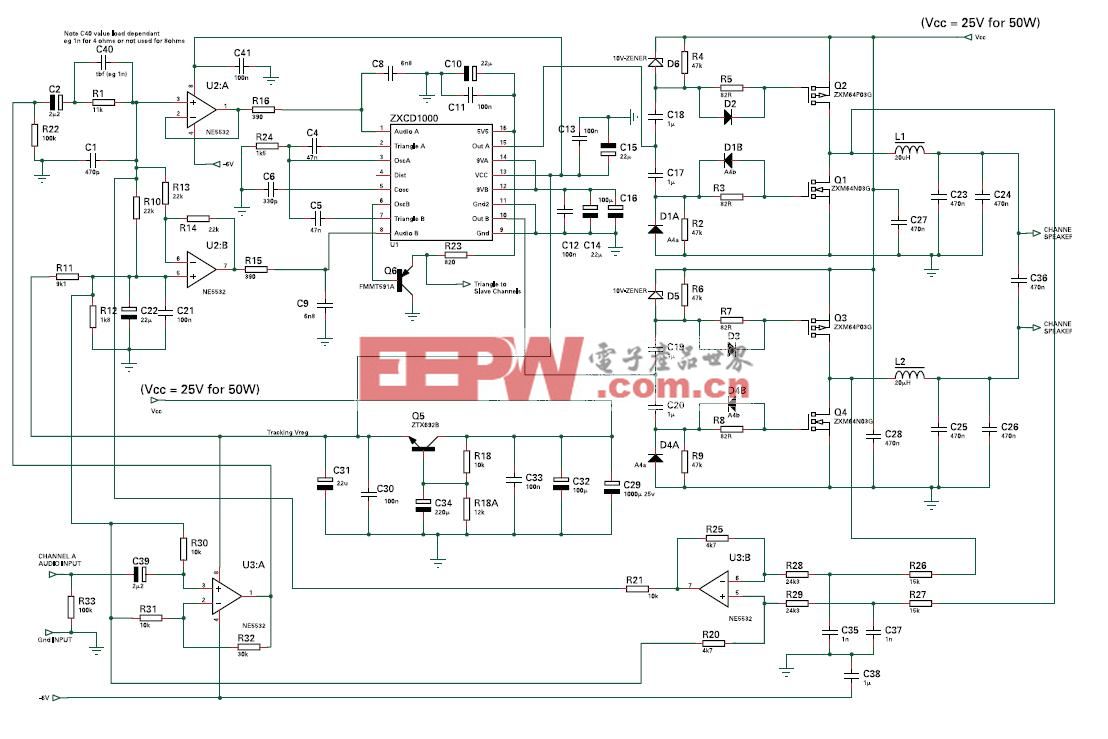

通过SOPC Builder软件包可以定制32位 Nios-II软核处理器和基本的Nios-II外设模块,如 UART控制器,定时器,FLASH控制器, SDRAM制器等。本文设计的硬件平台结构如图3所示。

本文引用地址://m.amcfsurvey.com/article/152380.htm

本文引用地址://m.amcfsurvey.com/article/152380.htm图 3所示虚线框内硬件部分均是在 FPGA内实现

该系统的嵌入式处理器 Nios-II是 Altera 公司推出的一个用户可配置的16 位或32 位精简指令集软核处理器。Nios-II处理器可以配置成最多支持 64个中断,包括外部硬件中断、内部中断以及 TRAP(调试中断)。Nios-II 处理器可以配置使用 32位内部定时器,通过软件控制写入控制寄存器的内容来获得定时工作,与一般的定时器工作原理相同,可以产生定时中断。

Nio-II嵌入式系统中采用 Avalon交换式总线在处理器、外围设备和接口电路之间实现网络连接,并提供高带宽数据路径、多路和实时处理能力。 Avalon交换式总线可以通过调用 SOPC Builder设计软件自动生成 [5]。

EDSLModem的核心部分即主收发器利用 FPGA中的逻辑单元编写自定义用户模块,并生成自定义 IP核,通过 Avalon总线接口与嵌入式处理器相连。该主收发器共包括了两个部分:EDSL成帧模块和 QAM调制模块。

在 SOPC系统中,除了以上部件,还有片上 ROM、内部定时器、 UART串行口、 SRAM、 Flash、以及以太网控制器 LAN91c111接口等系统部件皆由 SOPC builer自动生成。

评论