Modbus通信协议的FPGA实现

3.3 发送模块

发送模块包括发送控制模块,发送机模块,发送状态寄存器模块等。

发送机模块是基于普通UART发送原理设计,其发送过程如下:

(1)等待TDRE=‘1’,即等待发送数据寄存器(TDR)为空,随后TDR中载入一个字节数据,并把TDRE清零。

(2)根据波特率设置Sel_baud[1..0]对TDR里的数据进行奇偶校验计算。

(3)把TDR里的数据放入发送移位寄存器TSR的1~8位,TSR第O位放起始位(‘O’),TSR第9位放入奇偶校验位或者停止位(‘1’)。

(4)通过对TSR右移,一位一位地发送出9位数据比特,最后发送停止位(‘1’)。

3.4 CRC模块

CRC模块包括接收CRC控制模块,发送CRC控制模块,CRC产生模块三部分。

生成CRC的过程为:

(1)将一个16位寄存器装入十六进制FFFF(全1),将之称作CRC寄存器。

(2)将报文的第一个8位字节与16位CRC寄存器的低字节异或,结果置于CRC寄存器。

(3)将CRC寄存器右移1位(向LSB方向),MSB充零,提取并检测LSB。

(4)如果LSB为0:重复步骤(3)(另一次移位);如果LSB为1:对CRC寄存器异或多项式值0xA00l(1010000000000001)。

(5)重复步骤(3)和(4),直到完成8次移位。当做完此操作后,将完成对8位字节的完整操作。

(6)对报文中的下一个字节重复步骤(2)~(5),继续此操作直至所有报文被处理完毕。

(7)CRC寄存器中的最终内容为CRC值。

这种方式计算CRC值的时间比其他方式计算CRC(比如查表法等)的时间稍微要长,但是它节省了资源,比如查表法计算CRC需要一个数组来存放所有可能的CRC结果值。图5为对数据串“010300000001”(十六进制)CRC-16运算的仿真时序图,时钟周期为50 MHz,由图可见,整个计算时间在2.5 μs内,估算一个含有240个字符的消息,CRC校验总时间约为2.5μs×(240/6)=100μs,这样长的校验计算时间对于Modbus协议来说是完全可以接受的。

4 基于该接口的MODBUS从站协处理器实现

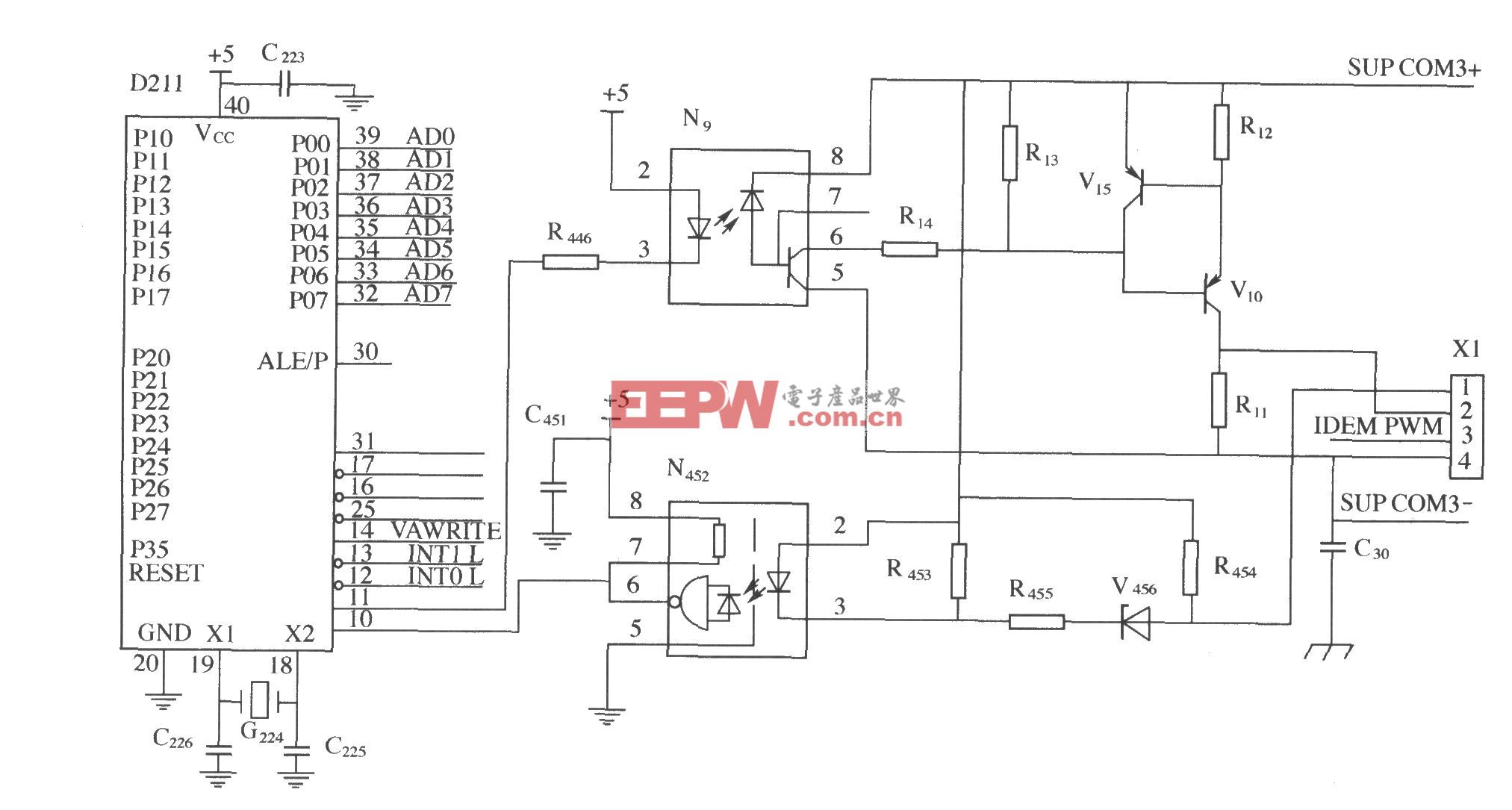

协处理器框图如图6所示。

从站协处理器控制模块程序控制过程如下:

(1)置CE_Modbus为‘1’,把MAX485芯片![]() 信号输出置低,即控制RS 485接口芯片处于接收状态。

信号输出置低,即控制RS 485接口芯片处于接收状态。

(2)等待一段延迟时间(RS 485接口芯片稳定时间),使能Modbus协议接口模块即置CE_Modbus为‘1’,并置接收Modbus协议帧模式。

(3)如果接收到一个完整的帧(消息),则转到步骤(4),如果没接收到一个完整的消息,一直处于等待状态。

(4)先置CE_Modbus为‘O’,再解释接收缓冲寄存器里消息,等待消息处理完毕,如果消息不是发往该从站或者为广播消息,则转到步骤(2);否则把![]() 信号输出置高,转到步骤(5)。

信号输出置高,转到步骤(5)。

(5)等待一段延迟时间,使能Modbus协议接口模块即置CE_Modbus为‘1’,并置发送Modbus协议帧模式。

评论