IDT70V9289的典型应用电路设计

由于本设计的数据传输率高达300Mbit/s,而IDT70V9289的容量仅有1024kbit,所以必须采取边读边写的方式缓冲数据。但是,IDT70V9289并不允许双端口对同一地址同时进行读和写,也没有像以前的SRAM(如IDT7024)那样设计操作忙逻辑,而是制定了一套读写规则。由于这套读写规则比较复杂,为了降低时序关系的复杂度,本设计将IDT70V9289分成容量相等的二个区域,把地址预存入Virtex-II XC2V250和CY7C68013的RAM中。

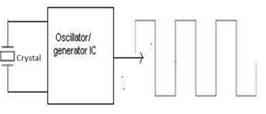

当CY7C68013向Virtex-II XC2V250传输数据时,将Virtex-II XC2V250和IDT70V9289的片选端置低电平以启动这二个电路,然后再向IDT70V9289发送数据,同时通过CLKOUT端向Virtex-II XC2V250的CLKIN发送时钟,以使Virtex-II XC2V250定时读取数据;当CY7C68013发送512kbit后,即改变A0R-A15R引脚的值,同时Virtex-II XC2V250也通过内置计数器定时改变A0L-A15L引脚的值,从而将CY7C68013的二个存储区域交换过来,然后再按上述方式进行读写,如此循环下去。只要读和写的平均速率保持一致,就可以保证数据可靠传输。应用电路框图如图4所示。这样做不但充分利用了二个端口可同时进行存取操作的特点,而且巧妙地避免了同时对同一地址进行读写操作的冲突,从而达到了设计要求。

当Virtex-II XC2V250向CY7C68013传输数据时,也可以通过片选端启动CY7C68013和IDT70D9289,其余过程与上面所述类似,不过由于CY7C68013有内置时钟,为了保持时间一致,此时的时钟仍由CY7C68013提供。

结论

IDT70V9289是IDT公司新推出的高速同步双口静态存储器,其容量为64k×16bit,具有设计简单,应用灵活等特点。

评论