2 电路仿真结果

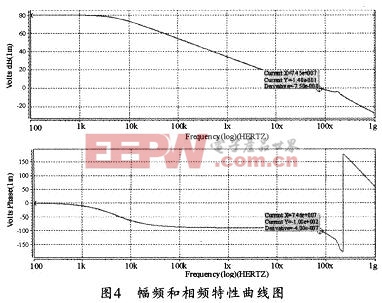

采用HSPICE电路仿真工具,并利用上华0.6μmCMOS工艺模型参数,可对电路进行仿真,仿真结果显示:该运放的开环直流增益为80 dB,相位裕度80度,单位增益带宽74 MHz。图4为其幅频及相频特性曲线。由图4可见,电路功耗为1.9 mW;差动输出范围为-2.48~2.5 V;电源电压为2.5 V。

3 结束语

本文给出了一种低电压全差分套筒式运算放大器的设计方法,同时对该设计方法进行了仿真,从仿真结果可以看出,在保证高增益、低功耗的同时,该设计还可以满足20 MHz流水线模数转换器中运放的设计要求。

评论