基于VHDL的99小时定时器设计及实现

3.2 显示模块

通过XUAN模块可完成BCD码的转化,再经DISP模块译码.然后输出给七段数码管。

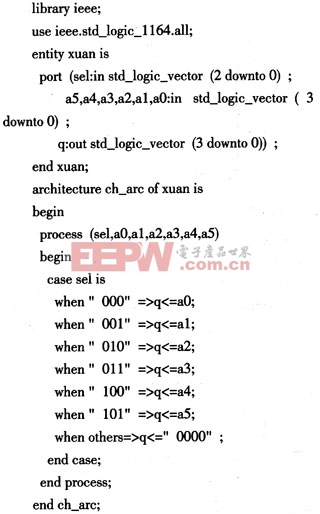

(1)XUAN模块

XUAN可产生四位BCD码输入,并从sel端输出。该模块的管脚图如图5所示。其源程序代码如下:

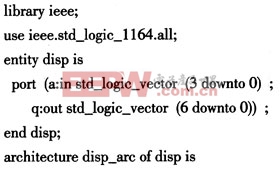

(2)DISP模块

DISP模块主要用于译码,可定义七段数码管显示的数字。其源程序如下:

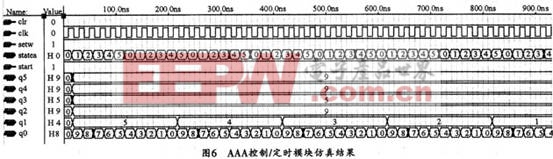

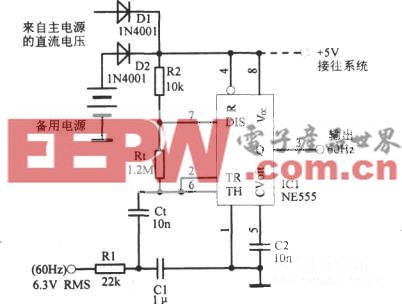

4 系统仿真及结果

图6所示是对AAA控制/定时模块的仿真结果。由此结果可见,当setw置“1”时,statea位选从0到5循环,分别代表六个数码管的位置。当start置“1”时,q5-q0进行借位减法。q5、q4表示小时,最高可到99小时;q3、q2表示分钟,最高59分钟;q1、q0表示秒,最高为59秒。

5结束语

本设计从总体要求出发,采用模块化设计方法,实现了长达99小时的定时设计。同时采用QuartusⅡ4.0仿真环境进行了仿真。结果证明,本系统可以实现理想的定时操作而且设计体现了人性化,具有较强的实际应用价值。

评论