基于FPGA 的UART 扩展总线设计和应用

2.2 UART 的逻辑设计

UART 的通信协议十分简单,以低电平作为起始位,高电平作为停止位,中间可传输 5~8 比特数据和1 比特奇偶校验位,奇偶校验位的有无和数据比特的长度由通信双方约 定。一帧数据传输完毕后可以继续传输下一帧数据,也可以继续保持为高电平,两帧之间 保持高电平,持续时间可以任意长。

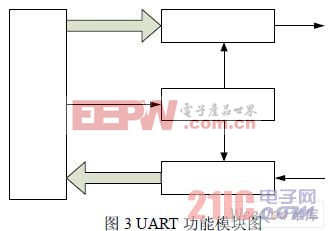

UART模块由SLAVE接口、波特率控制器、UART接收器和UART发送器构成。SLAVE 接口是为了实现WISHBONE 总线和功能模块之间的数据传输;UART 发送器的用途是将准备输出的并行数据按照基本UART 帧格式转为TXD 信号串行输出;UART 接收器接收RXD 串行信号,并将其转化为并行数据,但串并转换的时钟同发送器一样处理,收发设备间的时 钟是会累计的,会导致接收数据不正确,波特率控制器就是专门产生一个远远高于波特率的 本地时钟信号对输入RXD 不断采样,以不断地让接收器与发送器保持同步。

波特率控制器实际上就是一个简单的分频器。可以根据给定的系统时钟频率(晶振时 钟)和要求的波特率算出波特率分频因子。已算出的波特率分频因子作为分频器的分频数。 对于波特率发生器中的系数一般在FPGA 实现时往往是固定的,但对于不同的实现,这个 系数需要更改。波特率控制器产生的分频时钟,不是波特率时钟,而是波特率时钟的16 倍,目的是为了在接收事实进行精确地采样,以提出异步的串行数据。

UART 发送器由16 个字节FIFO 和信号发送器组成。FIFO 主要是起到数据缓存的作用, 信号发送器的核心部分由有限状态机实现的,实现伪代码如下:

case (状态机状态)

空闲状态:if ( FIFO 中有数据 )

状态机跳转到 FIFO 读取状态;

else

状态机保持空闲状态;

FIFO 读取状态:读取FIFO 数据,保存到移位寄存器;状态机跳转到开始位状态;

开始位状态:时钟计数,发送开始位;计数结束后状态机跳转到数据位状态;

数据位状态:时钟计数,发送数据,移位寄存器移位;计数结束后

if(移位寄存器内数据发送完毕)

状态机跳转到停止位状态;

else

状态机跳转到数据位状态;

停止位状态:时钟计数,发送停止位;计数结束后状态机跳转到 s_idle;

default:状态机复位到空闲状态;

endcase

UART 接收器包括了16 个字节FIFO、信号同步器和信号接收器三个部分。其中信号同 步器则是为了解决串行数据帧和接收时钟是异步问题,其它两部分和UART 发送器的中的 功能相似,只是数据传送的方向相反。

3 设备接口和驱动设计

3.1 设备接口设计

AT91ARM9200 芯片通过其静态存储控制器 (SMC)控制EP1K,而静态存储控制器 (SMC) 是控制外部静态存储器或外设的访问。 SMC 可编程地址达512M 字节。它有8 个 片选及一个26 位地址总线。16 位数据总线能配置与8 位或16 位外部器件连接。独立的读写控制信号允许存储器与外设直接连接。SMC 支持不同的允许单时钟周期存储器访问的访 问协议。它还提供外部等待请求能力。

因为 EP1K 内部设计使用的是8 位数据总线和8 位地址总线,所以AT91ARM9200 芯片与EP1K 相连的I/O 端口为 A[7:0],D[7:0],NRD 和NWR0。然而EP1K 内部采用 的WISHBONE 总线规范,其读写信号wb_we_o,高电平表示为写操作,低电平表示为 读操作。所以需要将NRD 和NWR0 进行相应的信号转换。而D[7:0]为双向端口IO, 所以在EP1K 的设计中采用三态门的设计。

评论