基于FPGA的CCD相机时序发生器的设计

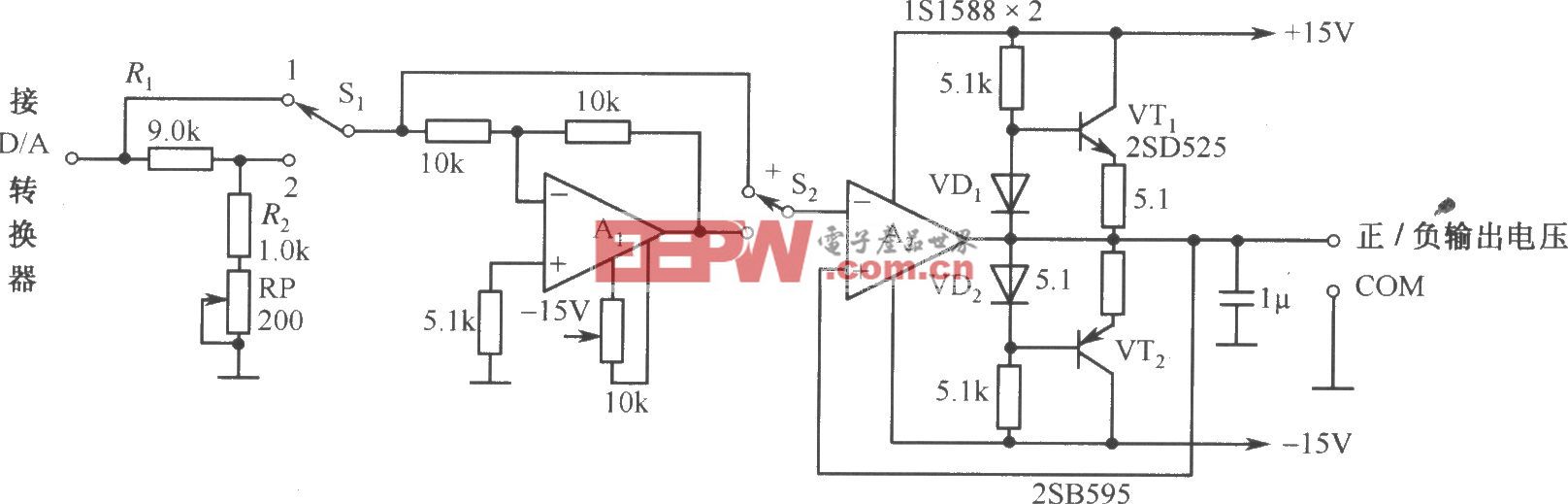

TDI-CCD的驱动时序控制比普通线阵CCD的驱动时序控制要复杂的多, IL-E2型TDI-CCD的时序控制包括各种直流电平控制和各种时钟脉冲序列控制。对于前者,主要包括供电电压VDD、输出栅电压VEST、溢出栅电压VOV、衬底电压VBB和级数控制偏置电压等;对于后者,主要包括行转移时钟脉冲TCK,像元移位读出时钟脉冲CR1、CR2,输出复位时钟脉冲RST,TDI方向移位寄存器驱动时钟脉冲CI1~CI4,级数控制时钟脉冲CSS6、CSS12、CSS24、CSS48。TDI-CCD工作时,在行转移时钟脉冲TCK为高电平期间,像元感光产生的信号电荷在TDI方向移位寄存器驱动时钟脉冲CI1、CI2、CI3、CI4的共同作用下,沿着TDI(TDI级数由TDI级数控制脉冲选为6、12、24、48、96中的一种)方向积累并转移到输出移位寄存器中;当TCK为低电平时,TDI-CCD在像元移位读出时钟脉冲CR1、CR2的作用下,输出复位时钟脉冲RST每来一个有效电平高电平时,TDI-CCD的输出信号OS端输出一个信号,直到信号输出完为止。之后TCK由低电平变为高电平,CI1、CI2、CI3、CI4也相应的变为有效电平,转移上一次转移完后像元感光产生的信号电荷,开始一个新的周期。这些时序控制的详细对应关系如图2所示。

图2 TDI-CCD时序详图

对于此TDI-CCD时序设计与普通线阵CCD时序设计存在以下几个突出特点。(1)在TDI方向存在4相移位寄存器驱动时钟,它们的周期与行周期一致,高电平脉宽t3应大于3μs, CI1的上升沿滞后于TCK的上升沿,CI2的下降沿滞后于TCK的下降沿,CI1、CI2的高电平脉宽至少有1μs的重叠。CI3、CI4在时序关系上分别为CI1、CI2的倒相。(2)此TDI-CCD的工作级数可以通过CSS6、CSS12、CSS24、CSS48四个级数选择信号进行控制,使其工作于96、48、24、12和6级。

3 时序发生器的原理组成和工作过程分析

时序发生器产生TDI-CCD、视频处理器和图像数据输出所需的各种时钟脉冲信号, 时序发生器在CCD成像单元工作中起着时间上同步协调的作用。它由时序控制器给出的指令和参数予以控制。时序控制器控制TDI-CCD工作时的行转移周期, 积分级数,控制指令和参数以串行数据的形式送至时序控制器中,时序发生器根据时序控制器给出的指令和数据产生TDI-CCD和视频处理器所需要的时钟脉冲信号: 行转移时钟脉冲、像元移位读出时钟脉冲、输出复位时钟脉冲、TDI方向移位寄存器驱动时钟脉冲、级数控制时钟脉冲、相关双采样时钟脉冲、A/D转换器采样时钟脉冲等。为了提高工作时的可靠性, 在时序控制器中控制指令和参数没有更新时, 时序发生器将按时序控制器中初始设置参数工作。

时序发生器的设计:时序发生器生成TDI-CCD、视频处理器和图像数据输出所需要的各种时序。所有时序是由主振脉冲序列通过逐级分频后的脉冲序列进行逻辑和组合运算产生的。它们之间满足严格的相位关系, 这是相机系统协调工作的基础。时序发生器的功能框图如图3所示。相机系统一通电就应保证立即工作在内部默认方式, 这样就能够马上判断系统是否正常。如果外部或内部设置指令无效, 系统也返回默认方式, 这是相机系统可靠性的体现。时序发生器所产生的各种时钟由VHDL 语言完成。

图3 时序发生器功能框图

评论