一种基于FPGA并行流水线的FIR滤波器设计方案

FPGA有着规整的内部逻辑块阵列和丰富的连线资源,特别适合细粒度和高并行度结构特点的数字信号处理任务,如FIR、FFT等。利用FPGA实现FIR滤波器的设计过程,并且对设计中的关键技术一分布式算法进行详细描述。

FIR滤波器的结构主要是非递归结构,没有输出到输入的反馈。并且FIR滤波器很容易获得严格的线性相位特性,避免被处理信号产生相位失真。而线性相位体现在时域中仅仅是h(n)在时间上的延迟,这个特点在图像信号处理、数据传输等波形传递系统中是非常重要的。此外,他不会发生阻塞现象,能避免强信号淹没弱信号,因此特别适合信号强弱相差悬殊的情况。

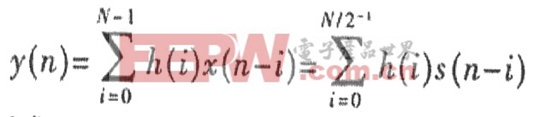

通常采用窗函数设计FIR滤波器方法简单,但是这些滤波器的设计还不是最优的。首先通带和阻带的波动基本上相等,另外对于大部分窗函数来说,通带内或阻带内的波动不是均匀的,通常离开过渡带时会减小。若允许波动在整个通带内均匀分布,就会产生较小的峰值波动。对于线性相位因果FIR滤波器,它的系列具有中心对称特性,即h(i)=±h(N一1一i)。令s(i)=x(i)±x(N一1一i),对于偶对称,代入式(1)可得:本文引用地址://m.amcfsurvey.com/article/192107.htm

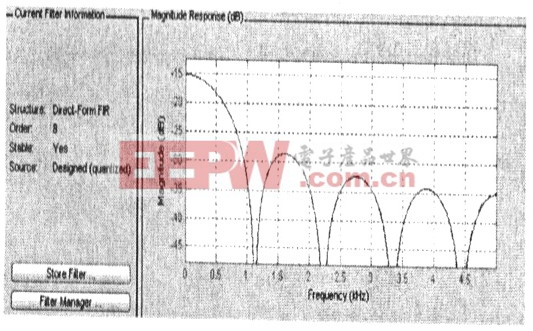

根据要求,要设计一个输入8位,输出8位的9阶线性相位FIR滤波器,所以采用图2(a)的方式,其中输入信号范围为:[99,0,0,O,99,O,0,0,99,O,0,0,99,…],此滤波器Fs为lOOkHz,Fc为10kHz。利用MATLAB设计计算9阶FIR滤波器系数和幅频响应如下:

整数化后,可得FIR滤波器的参数为:[4c,4f,50,52,52,52,50,4f,4c:]

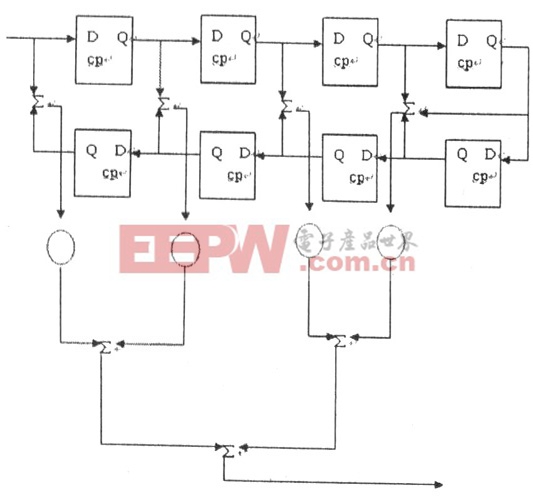

根据以上所说的思路,可以将FIR滤波器的原理图设计如下:

下面对各加法器乘法器的输出位数进行分析,对第一级加法器,输入为8位,输出统一为9位,最后一个加法器为三输入端,输入都为8位,输出为10位。对各个乘法器进行分析,第一个乘法器为4c,因此输入为9位,输出为15位。第二个乘法器为4f,输入为9位,输出为15位。第三个乘法器为50,输入为9位,输出为15位。第四个乘法器为52,输入为10位,输出为16位。乘法器输出结果两两相加,第一个加法器输入都为15位,输出为16位,第二个加法器,输入分别为15位和16位,输出为16位。最后这两路输出之和为16位。将后8位舍去,然后相加,总输出为8位。至此,所有器件的输入输出都已经判定。下面进入模块设计阶段。

评论