多总线融合式通用自动测试系统设计

该基本型能够适应多种测试需求,从以上各方案中可以得出在以此基本型建立自动测试系统时,可加入总线,也可不配置总线建立小型测试系统,基于此基本型建立测试系统方法如图2所示。本文引用地址://m.amcfsurvey.com/article/195049.htm

1.3 转接口设计

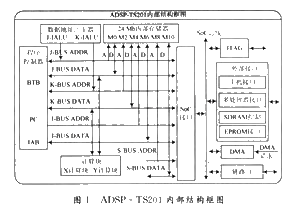

要实现PC/104主机与外界的通讯,转接口的设计是其中非常重要的环节之一。而在本方案中PC/104总线转MXI总线接口的设计好坏是关乎着整个系统能否实现高速测试的关键。复杂可编程逻辑器件(CPLD)几乎适用于所有的阵列和各种规模的数字集成电路,它以其编程方便、集成度高、速度快、价格低等特点越来越受到设计者的欢迎。转接口的设计采用CPLD即可完成要求。接口设计方案如图3所示。

通过对PC/104总线和所选总线的时序、信号、地址、数据等方面的需求分析,用CPLD设计接口模块,实现总线握手和数据传输功能。C-PLD部分电路原理如图4所示。

PC/104使用的总线资源主要是I/O控制和中断,具体信号如下:A[0..19]是PC/104的10位地址总线;D[0..7]是PC/104的8位双向数据总线;IOR,IOW分别是总线I/O端口读、写信号;AEN是允许DMA控制地址总线、数据总线和读写命令线进行DMA传输以及对存储器和I/O设备的读写;IOCHRDY是I/O就绪信号,I/O通道就绪为高;SYSCLK是系统时钟信号,使系统与外部设备保持同步;IRQ3是中断信号。PC104部分电路原理如图5所示。

1)数据传输(PC/104→MXI) PC/104需要传送数据时,PC/104置位AEN信号,通过发送地址与数据总线向CPLD发送数据,此时IOW引脚置低电平(有效)。当CPLD接收到正确数据后,驱动MXIbus的地址选通信号AS,获取地址信息后,再驱动MXI的数据选通信号DS,置位读写信号WR取走数据,通过MXI的应答信号DTACK来判断数据是否传输完毕,完毕则发送下一个数据,MXIbus采用的是地址数据总线复用形式。

2)数据传输(MXI→PC/104) 当MXI向CPLD传送数据时,置位AS,驱动数据选通信号DS,并且WR有效,发送数据。CPLD收到数据后,通过IRQ3向PC/104发送中断申请,PC/104收到中断信号后,首先置位AEN,然后IOR变低电平,从CPLD寄存器口地址读取数据。

评论