动态偏振控制器驱动电路分析

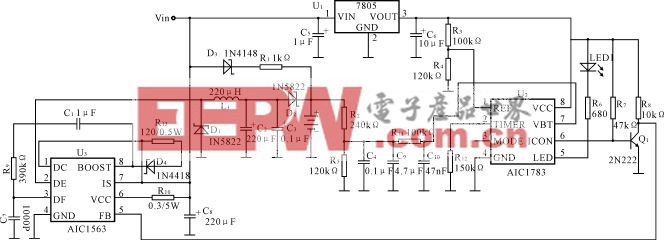

LTC1668工作在士5 V双极性电压供电情况下,其参考电压由内部提供,输出采用单端电流输出模式。宽带放大器LT1812完成电流一电压转换,最终输出符合要求的正弦信号。

2.3 软件设计

FPGA是驱动电路的控制核心。FPGA接收ADC转换的光强信息数据,并传送给DSP;再根据DSP计算所得的数据(即正弦驱动信号的频率f)判断是否符合要求,若符合要求则进入DDS子模块,得到幅度码并发送给LTC1668,以输出需要的正弦波。FPGA主模块流程图如图6(a)所示。

式中:fo是输出频率;fref为DDS参考时钟频率,由FPGA将晶振输入时钟经内部锁相环分频后产生。

由相位步进累加可得到相位码,再寻址波形存储器即可完成相位——幅度转换,得到相应的幅度码,输出给主模块。由于驱动信号为正弦波,波形存储器直接调用FPGA内部模块sin_COS_lookup_table,输入与输出数据位宽均为16位。DDS子模块流程图如图6(b)所示。

2.4 实验测试结果

实验时设定4路正弦驱动信号V1,V2,V3,V4的频率分别为f1=2 000 Hz,f2=1 000 Hz,f3=1 800 Hz,f4=1 500 Hz。

示波器上观测的波形如图7所示。

波形使用双通道示波器观测,2通道探头设置为10档。从图7中可以看出,输出波形较为稳定。如果在FPGA程序内增大sin_COS_lookup_table模块的输入数据位宽,也即增大采样点数,可以得到精度更高的输出波形。

3 结 语

实验测试结果表明,所设计的调制电路能够输出4路频率可调的正弦信号,输出信号稳定,控制灵活,工作性能可靠。该方法思路简单,采用Verilog语言设计并调用FPGA内部模块,设计灵活透明,且外围电路较为简易,具有良好的实用性和性价比。

评论