影响EMC的因素和降噪技术

滤波技术包括:

* 对电源线和所有进入PCB的信号进行滤波

* 在IC的每一个点原引脚用高频低电感陶瓷电容(14MHz用0.1UF,超过15MHz用0.01UF)进行去耦

* 旁路模拟电路的所有电源供电和基准电压引脚

* 旁路快速开关器件

* 在器件引线处对电源/地去耦

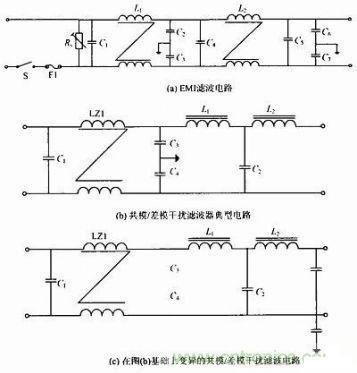

* 用多级滤波来衰减多频段电源噪声

其它降噪设计技术有:

* 把晶振安装嵌入到板上并接地

* 在适当的地方加屏蔽

* 用串联终端使谐振和传输反射最小,负载和线之间的阻抗失配会导致信号部分反射,反射包括瞬时扰动和过冲,这会产生很大的EMI

* 安排邻近地线紧靠信号线以便更有效地阻止出现电场

* 把去耦线驱动器和接收器适当地放置在紧靠实际的I/O接口处,这可降低到

PCB其它电路的耦合,并使辐射和敏感度降低

* 对有干扰的引线进行屏蔽和绞在一起以消除PCB上的相互耦合

* 在感性负载上用箝位二极管

评论