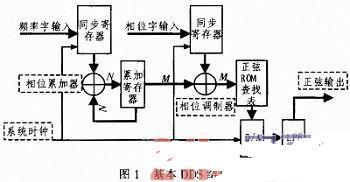

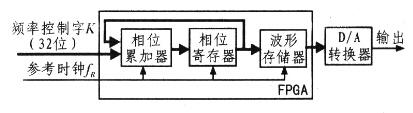

基于DDS+PLL技术的高频时钟发生器

4 结语

本文提出了一种新的频率发生器设计方案。DDS+PLL频率合成系统由于具有其他频率合成方法无法比拟的优点,近年来得到广泛的应用。基于DDS芯片AD9854的高精度频率信号发生器设计的时钟信号源,已经用于科研项目中。可以看到,当要求得到既有高的频率分辨率,又有较快的转换速度和较低噪声的高频甚至微波信号时,DDS+PLL技术就显现出了强大的生命力。

参考文献

1]KroupaVF.Phaseandamplitudedisturbancesindirectdigitalfrequencysynthesizer[J].IEEEInternatiONalfrequencycontrolsymposium,1997:975979

2]张厥盛,郑继禹,万心平锁相技术[M].西安:西安电子科技大学出版社,1994

3]白居宪低噪声频率合成[M].西安:西安交通大学出版社,1995

滤波器相关文章:滤波器原理

滤波器相关文章:滤波器原理

负离子发生器相关文章:负离子发生器原理

分频器相关文章:分频器原理

电荷放大器相关文章:电荷放大器原理

尘埃粒子计数器相关文章:尘埃粒子计数器原理

混频器相关文章:混频器原理

鉴相器相关文章:鉴相器原理

晶振相关文章:晶振原理

脉宽调制相关文章:脉宽调制原理

离子色谱仪相关文章:离子色谱仪原理

锁相环相关文章:锁相环原理

评论