基于Verilog HDL语言的CAN总线控制器设计及验证

接着使用ModelSim软件对所设计的各个模块和整个CAN总线控制器进行了功能仿真,仿真结果表明达到了设计目标。

2 测试验证

本文最后设计了CAN总线控制器的测试程序,其目的是模拟一块微处理器对CAN总线控制器进行读写操作,从而实现对CAN总线控制器的寄存器访问,完成总线收发功能。在该测试程序编写中,各个功能基本上以任务的形式实现,进行不同的仿真时只需调用相关的任务模块。图8为验证程序的组成框图。

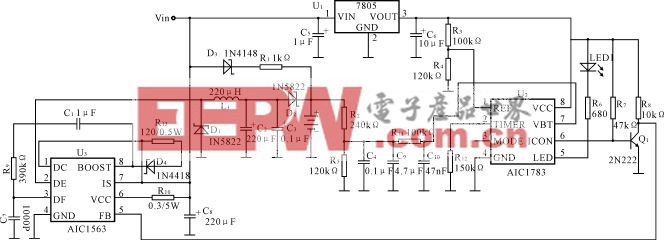

仿真验证完成以后将其HDLCAN总线程序下载到FPGA中进行测试,目标芯片采用Cyclone系列的EP1C6Q240C8,为了验证所设计的FPGACAN总线控制器,还设计了一款基于该FPGA的CAN总线控制器的节点电路,然后利用所设计的节点电路与其他3个利用SJA1000作为控制器的CAN总线节点进行了通信测试。所有的节点使用AT89S52单片机作为节点微处理器,PCA82C250作为收发器,测试结果表明下载到FPGA中的控制器程序工作正常,实现了预计的CAN总线通讯功能。测试网络示意图如图9所示。

测试时,按动节点1上的开关并将该状态发送到节点2,在节点2上能显示对应的状态,反之也可。同时也可在节点2通过键盘输入某一代码,而在节点1上的数码管上显示相应的结果。该实验结果表明下载到FPGA中的控制器程序工作正常。

3 结语

本项目利用VerilogHDL语言设计了一款CAN总线控制器芯片,并使用ModelSire软件对所设计的CAN总线控制器进行了功能仿真;之后为了验证设计,还编制一个验证程序,并将验证之后的设计配置到了FPGA中;最后用所设计的基于FPGA的CAN总线控制器制作了CAN节点,并与其他采用SJA1000为控制器的CAN节点进行了通讯测试,实现了CAN总线良好的工作,验证了设计的正确性。

评论