交换接口控制器的可扩展设计

对于终端突发数据,如果在最后的TLP字中的所有字节都有效或与末块终接(terminal with end pad),则PI2 SAR代码就是“终端”,来表示最后的字中有效字节的数目。

如果SPI4.2突发数据包长度超过ASI TLP有效载荷长度的话,PI2 SAR被用于将SPI4.2数据包分段和重组。接收到的SPI4.2突发数据包在桥接中被分段为ASI接口支持的有效载荷的长度(图4)。

至于封装,三个TLP的PI2 SAR代码被分别设置为代表“初始”、“中间”和“终止”或“末块终接”。对于重组,来自每一个关联域的AS片段被重组成完整的数据包。一旦获得完整的数据包,它就被映射到一个SPI4.2通道并在突发数据包中输出。来自SPI4.2不同通道的突发数据包可以交织在一起。

映射流量类型、等级和目的端口

交换接口必须与数据一起传输若干重要属性。这些属性包括流量类型(单播或多播)、等级、目的端口和拥塞管理。这些参数都在AS中得到支持。然而,在SPI4.2中,该信息被映射在SPI4.2通道编号中或SPI4.2有效载荷内的专有报头。

SPI4.2利用三级拥塞指示(空虚、未满、饱满)进行基于信用量的流控制。通过预置与空虚和未满状态相对应的最大突发数据量(Maxburst1和Maxburst2),发送器会再次装满信用量。

|

图5:典型单10Gbps端口中的双网络处理器及配备专用FIC的全双工线卡。 |

ASI具有多个流控制选项:VC,它是一个基于信用量的流控制;用于源速率控制的令牌桶;按照类或者流队列的基于状态的流控制。

桥接内的拥塞管理是桥接架构和缓冲机制的不可缺少的组成部分。桥接可以采用两种基本架构,或者采用具有很少或没有缓冲的直通(flow-through),或者每一个接口采用单级或两级缓冲。

在直通架构中,流控制信息被生成并在外部作用于桥上。该方法简化了桥的设计,但是,增加了源和流控制的目的端口之间的延迟时间,因此可能需要增加缓冲资源。

在有缓冲的架构中,桥接本身遵照流控制信息,因此需要内部缓冲。内部桥接缓冲可以由两个接口共享(单级),或每一个接口配备自己的关联缓冲器,称为两级缓冲处理。

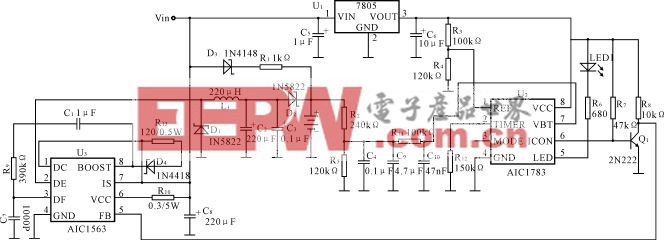

入口网络处理器接收端口被配置为物理器件接口的SPI4,而发送端口被配置为交换接口的SPI4.2,连接到专有的FIC(图5)。FIC支持全双工SPI4.2接口和多达24个速率为2.5Gbps的全双工PCI Express SERDES(串行化/解串化)链路,一个10Gbps的全双工链路端口需要4个SERDES链路。不用的SERDES链路可以通过器件配置寄存器的设置来关闭供电。在这个10Gbps的例子中,NPU通过PCI本地总线接口配置EP1SGX40内部的“配置和状态”寄存器。

专有FIC参考设计

专有FIC参考设计平台是采用英特尔的IXDP2401先进开发平台设计和验证的。AdvancedTCA机架把连接AdvancedTCA高速交换接口的两个IXMB2401网络处理器承载卡(carrier card)互连起来,承载卡是采用一块IXP2400处理器设计的PICMG3.x兼容板。承载卡采用标准组件结构,包含4个子卡槽位和一个可选交换接口子卡槽位,以便连接到AdvancedTCA背板上区域2的交换接口引脚。

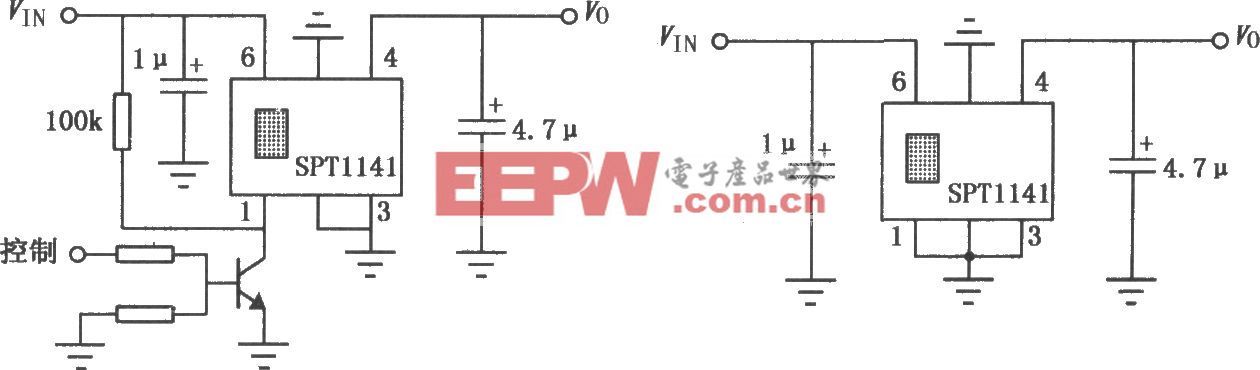

专有的、基于FPGA的交换接口子卡(mezzanine card)槽位的设计使其可插入承载卡,并提供一个可重配置的FIC和可选的流量管理开发板。FIC使处理器与AdvancedTCA交换结构相互连接。利用包含兼容PCI Express与XAUI的多通道收发器的可重复编程器件,可以提供可扩展的开发平台,以便快速设计和验证2.5Gbps到10Gbps的AdvancedTCA FIC设计(图6)。

工作模式

参考设计的主要工作模式接收来自处理器入口端的32位SPI3或16位SPI4.2数据,通过FPGA集成收发器将数据流传输到AdvancedTCA背板,并将背板数据流通过32位SPI3或16位SPI4.2接口传回处理器的出口端。

集成收发器经由处理器的SlowPort出口来配置。参考设计支持若干其它工作模式,包括SPI4.2接口环回、ASI接口环回、流量管理、交换结构数据包生成和监测。

FPGA和结构化ASIC FIC

采用专有的多FPGA和结构化ASIC技术,可以开发可扩展的PCI Express、ASI桥和端点。内建兼容PCI Express收发器的高密度、高性能的FPGA,可以提供:1. 具有可扩展的2.5链路的整体解决方案;2. 对每一个通道运行速率高达1Gbps的接口进行动态相位校正(DPA);3. 多种封装选择和高达40,000逻辑单元的密度选项。

|

图6:功能模块框图。 |

可选的FPGA结合独立的兼容PCI Express的SERDES,如PMC-Sierra的PM8358 QuadPHY 10GX器件可用于对成本的关注超过对性能和扩展功能需求的应用,从而提供低成本的1x、2x和4x(路)灵活的解决方案。高密度、高性能FPGA与独立的、兼容PCI Express的SERDES的结合,可被移植到专用的结构化ASIC,以提供所需要的最高密度、最快性能和最大数量的应用。

评论