无线传感器网络节点模块化接口电路设计

2 SPI接口电路设计

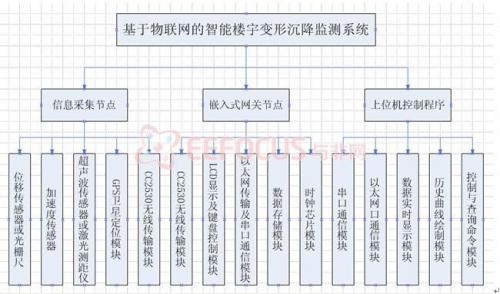

数据存储管理系统以单片机和可编程逻辑器件组成核心控制器。可编程逻辑器件CPLD依据其编程灵活、易修改的特点,配合单片机在其内部扩展SPI接口电路,不仅简化了接口和控制,且提高了系统的整体性能及系统扩展性。

SPI接口电路设计分两部分:

(1)硬件部分:CPLD内扩展SPI接口框图如图2。在CPLD内部编写双向IO总线、地址锁存译码电路、时钟发生器、接收和发送数据移位寄存器、传输结束标志SPIF产生器等电路完成SPI接口电路设计。READY1为与从机(冲击波模块等)通信时状态标志位,用于当主机与从机通信时查询使用,READY1为1时,可读取冲击波数据。

当单片机发送数据时,IO总线首先发送地址码,地址锁存译码电路生成数据装载使能片选信号,之后IO总线待发送字节锁存到数据寄存器SPDR,同时Sek时钟发生器产生8个Sek时钟,SPDR移位寄存器在Sek的时钟沿把待发送字节从MOSI顺序移出,同时把MISO引脚数据移入SPDR寄存器,Sek计数器计数到8个Sek时钟后,产生SPIF传输结束标志,单片机读取SPIF标志是否为1,判断一字节时候传输完毕。

(2)软件部分:单片机为主控制器,首先查询从机状态标志位READY是否为1,判断是否可以与从机通信。从机准备就绪时,单片机可装载1字节发送数据,启动CPLD内部SPI接口电路,查询并等待SPI传输结束标志位SPIF为1,完成一字节数据传输,如此重复。图3、图4为主机发送与接收1字节流程图。

3 试验结果与分析

图5为逻辑分析仪捕获CPLD扩展SPI接口电路读取冲击波模块数据时波形。

bit8:READY信号,从机高电平时主机读取数据;bit9:Sck时钟信号,主机查询READY为高时装载发送字节,并产生8个Sek时钟,启动SPI传输;bit10:MOSI,主机输出端口;bit11:MISO,主机输入端口,Sek上升沿读取数据,连续两个周期读取的数据分别为0x07(000001 11),0Xb0(10110000),两周期时间间隔为20.400us,传输速度可达4×105bps,满足系统要求。

结束语

为了满足系统测试任务,无线传感器节点采用模块化设计,各功能模块通过SPI接口链接。由于系统功能要求,使一个模块与多个模块链接通信,其接口电路SPI工作在不同的主从机模式,使用单一SPI接口主从切换,势必降低模块间通信速度与灵活性。依据可编程逻辑器件CPLD有其编程灵活、易扩展性,在模块内部扩展专用SPI接口,试验证明SPI接口电路设计,有简化模块间连接、提高通信速度、系统扩展性强,以及提高系统整体性能的特点。

评论