信号完整性分析中抖动的分类

一、峰峰值抖动、均方根抖动

过去多年来用于量化抖动的最常用的方法是峰峰值抖动(Peak-to-peak Jitter)和均方根抖动(Root-Mean-Square Jitter,抖动直方图或者抖动分布的1 或者RMS值)。但是由于随机抖动以及非固定抖动的存在,使得抖动的峰峰值随着观察样本数量的增加而增加,因此说峰峰值抖动参数用于衡量固有抖动会很有效,但是衡量随机性抖动却会出现很大误差;相同的道理,由于固有抖动及非高斯性抖动和噪声的存在,使得抖动的直方图或者分布图不呈现完全的高斯分布,因此统计得到的抖动的1σ或者RMS值不等于真实高斯分布的1 值。

峰峰值抖动和均方根抖动均是对某一类抖动的统计分析指标。

二、相位抖动、周期抖动、相邻周期间抖动

由于时钟系统是数字电路系统非常关键的一部分,直接决定了数据信号发送和接收的成败,是整个系统的主动脉,因此时钟的抖动一直备受关注。描述时钟系统的抖动参量一般分为三类,即相位抖动(Phase jitter)、周期抖动(Period jitter)、相邻周期间抖动(Cycle to cycle jitter).

1、相位抖动

在数字系统中,两个逻辑电平之间的切换通常伴随着快沿的出现,这些边沿在时序上的不稳定性就叫做相位抖动(phase jitter,有时也叫累积抖动,accumulated jitter,指实际边沿位置与理想边沿位置的偏差,以时间为单位,也可以换算成弧度,角度等);相位抖动是相位噪声在数字域的等效体现,它是离散量,因此只有当边沿存在时候才有定义。

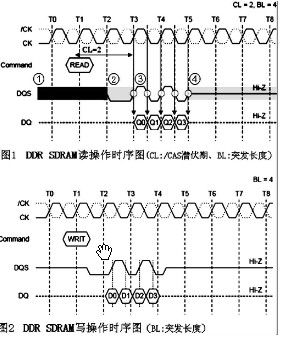

理想边沿位置一般定义在数字信号一个比特位时间间隔的整数倍位置处。如下图1所示为某一

不会直接使用时钟的边沿来保证时序关系,而是看周期的稳定性,也就是周期的抖动,有时候时钟周期越长,可能带来保持时间余量不足的问题,这个时候就需要测量周期抖动;而相邻周期间抖动常常可以用来衡量时钟分频器的稳定性。总之,这三种抖动都是衡量时钟本身性能的指标,在不同的应用背景下需要关注不同的指标,通常时钟芯片的手册会给出对时钟的抖动指标要求。

分频器相关文章:分频器原理

评论