一种基于CCD技术的钢管长度测量系统设计

2 系统组成及各部分功能

该测量系统主要由光源、CCD传感器、CCD驱动电路、FPGA可编程器件、信号调理电路、LCD显示电路、RS-485通信电路以及键盘输入电路等部分构成,其组成框图如图2所示。

1)FPGA(EP3C) FPGA是该系统的核心部分,一方面生成CCD驱动信号,控制CCD传感器完成数据的采集,另一方面滤波计算经调理电路A/D转换后输入信号,实现数据处理。然后通过控制LCD显示电路和RS-485通信电路实现数据的显示与传输。若有需要,还可以扩展其功能,譬如当段长满足配尺长度时,控制剪刀进行剪切,并记录剪切段长。

2)CCD传感器驱动电路 该驱动电路是CCD器件应用中的关键技术之一,主要是为了生成满足器件工作时的驱动时序脉冲,本系统采用FPGA实现对线阵CCD器件TCDl206SUP的驱动。

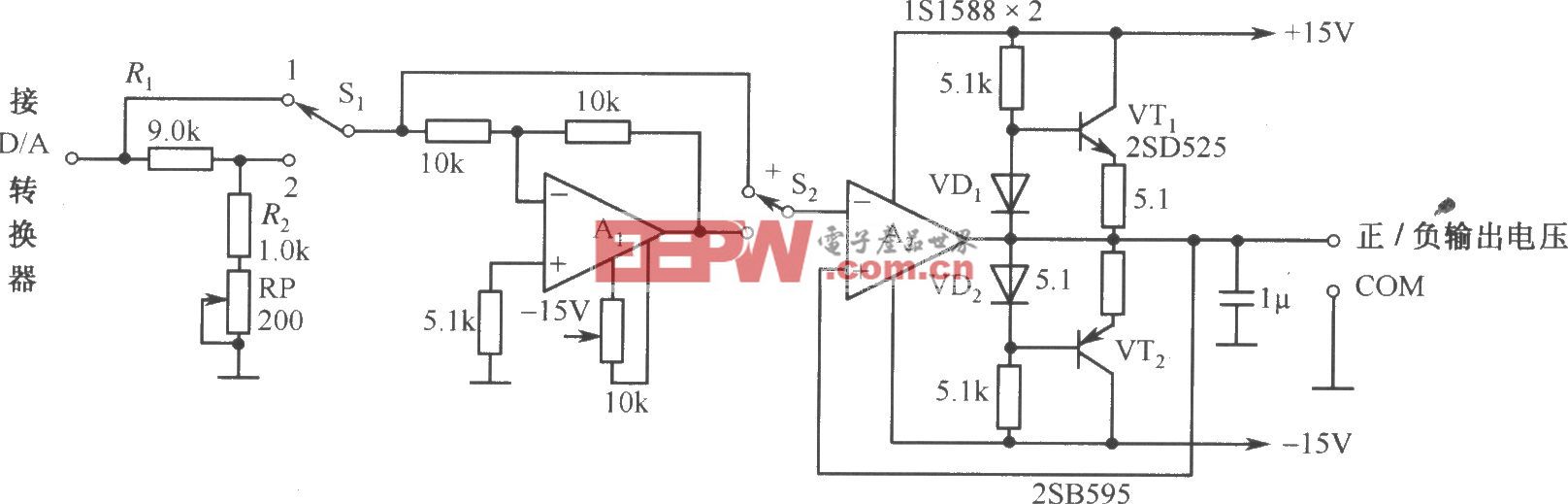

3)信号调理电路 传感器与微处理器之间的转接部分,由于传感器采集到信号一般能量弱,干扰强,且为模拟信号,所以调理电路的主要功能是对信号进行滤波、放大以及A/D转换等处理。

4)LCD显示电路 实现数据的显示功能,使操作人员能了解实时测量数据,并对其作出相应处理。

5)RS485通信电路 现场的测量仪器和上位机的通讯距离较远,所以,该系统采用RS-485通信。当前工业现场总线中以RS-485使用最为普遍,这种网络结构因硬件设计简单、控制方便、成本低廉、通信速率高等优点而应用广泛。

3 系统各部分功能实现

3.1 CCD驱动电路

该驱动电路选用独立脉冲源。由晶体振荡器构成时钟发生电路,输出频率为4 MHz的时钟脉冲,经4分频器得到频率为l MHz的时钟脉冲,再经脉宽调制器合成占空比为1:3的复位脉冲φR,时钟脉冲φ1为0.5MHz,由脉冲信号8分频得到,φ2由φ1反相产生,如图3所示。

3.1.1 分频器的实现

该设计需要对4 MHz的时钟脉冲分别进行4分频和8分频,在FPGA设计中,分频器可采用图形输入设计,运用触发器或计数器来实现不同制式的分频;也可运用VHDL代码输入通过不同的算法实现设计。

分频器相关文章:分频器原理

评论