关于常用通信接口技术的探讨

对于第一种接口,位于同一块电路板的网络处理器芯片组和交换架构间的接口可用CSIXLevel1接口实现。该接口采用CSIXLevel1包格式,包括为交换架构提供路由指令的报头,以及用于误差检测及纠正的报尾,还包括数据载荷本身。控制CSIX规范的网络处理器论坛将进一步完善该规范,增加从一个NPU芯片组通过交换芯片传至另一个NPU芯片的额外指令。这将成为CSIXLevel2规范的最主要推进力。该规范还定义了每个方向中使用至多128个HSTL一类I/O的电气互连,其源同步时钟频率高达250MHz。CSIXLevel1协议与CSIXLevel1电气规范无关,无论NPU芯片组和交换架构间的经由背板的通信采用何种电气标准,仍可使用CSIXLevel1协议。

对于第二种接口,即NPU芯片组与交换架构间需要在通过背板通信,仍然可以使用CSIXLevel1协议,但这种电气接口并不合适。信号将穿过连接器,从端口卡到达系统背板,经过数英寸到达另一个连接器,然后进入交换卡。有诸多原因使得越来越多的设计者选择具有嵌入式时钟的串行接口来实现这些连接。首先,串行接口可最大限度地减少电路板与背板连接器的引脚数,从而可减小插拔力及对操作系统中电路板的可能损害。其二,在信号中嵌入时钟和数据的串行接口可完全避免时钟偏移问题。时钟偏移是PCB中数英寸长的并口所面临的主要问题。其三,串行信号的背板设计者还可提高传输速率,因为不存在时钟偏移,也就没有对未来性能的限制。

被成功用作串行背板标准的接口是XAUI,它是为10千兆以太网开发的。该规范适用于通道排列电路,无论四通道轨线长度是否匹配,符合XAUI的器件均能接收无误差数据。该接口使用差分电流模式逻辑信令,它还采用交流耦合模式,允许电路板间的参考电压不同。

控制板接口

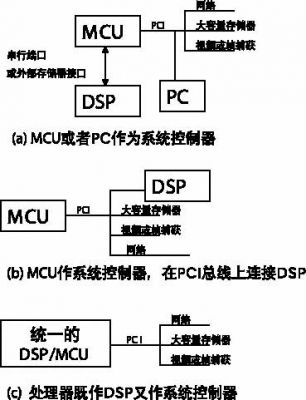

目前本文所提到的接口都用于数据通道,即数据从光纤传输介质到达交换架构,然后返回光纤通道。但由于通信系统具有复杂的控制板,负责统计数据收集、流量监视、系统管理及维护等功能,因此需要强大的处理能力运行软件以实现这些功能。这些构建控制板处理器的接口正如设想的那样,与数据通道的接口明显不同。数据通道接口主要用于在两个器件间传输数据(即点对点链接),控制板接口则是与具有不同元件的一个或多个微处理器相连接:背板收发器、DSP、数据板器件的控制端口等。实现这些灵活的互连需要完全不同类型的接口。

这类系统过去都是围绕多点复接的中心总线构建的。实现PCI总线架构的32位/33MHz及最近采用的64位/66MHz标准已经用于通信系统中。最近64位/133MHzPCI-X更用于高端服务器。但是,由于数据板处理的带宽已经增加,控制板的带宽也要提高。很多设计者发现共享总线带宽不足以满足多个器件的需求。因此,出现一类新型接口。

这类新接口采用点至点连接,用源同步时钟减少时钟偏移。差分信令可提高数据传输率,减少交换噪声和功耗。但真正的创新在于使用交换架构或通道器件,实现控制应用中所需的多点互连。

已获得Motorola及RapidIO贸易联合会支持的RapidIO是使用交换架构实现点至点链接的接口。

该接口的传输层规定数据如何封装在包中,每个包都具有数据源和目标信息,交换架构将数据包送往合适的?用250MHz~1.0GHz双数据速率。此外,串行RapidIO可使用具有8b/10b编码的1通道或4通道数据,嵌入时钟达3.125Gb/s,它还具有CML差分信令。

AMD及HyperTransport联盟开发的HyperTransport使用通道器件实现点至点链接。数据以包的形式传输,每个包均包括数据源和目标信息。接收数据的通道器件按照数据包报头确定是将数据传至链中的下一个器件,还是直接处理数据。目前的HyperTransport规范需要宽度为2~16位的并行数据。未来规范可支持更高速率。PMC-Sierra和BroADCom已经为HyperTransport通信产品推出基于MIPS的处理器。

PCI-SIG已经推出高速率PCI-X。它们使用与最初PCI-X相同的64位总线带宽,可支持双数据速率和四倍数据速率。PCI-X533是速率最快的版本,最大总计带宽达34.1Gb/s。

PCI-X的传输通讯协议、讯号和标准的接头格式都与PCI一并兼容,可以使3.3V的32位PCI适配卡可以用在PCI-X扩充槽上。当然如果你愿意,也可以将64位PCI-X适配卡接在32位PCI扩充槽上,不过,频宽速度将会大减

评论