选择合适的微控制器策略

高集成度与中断延时和安全

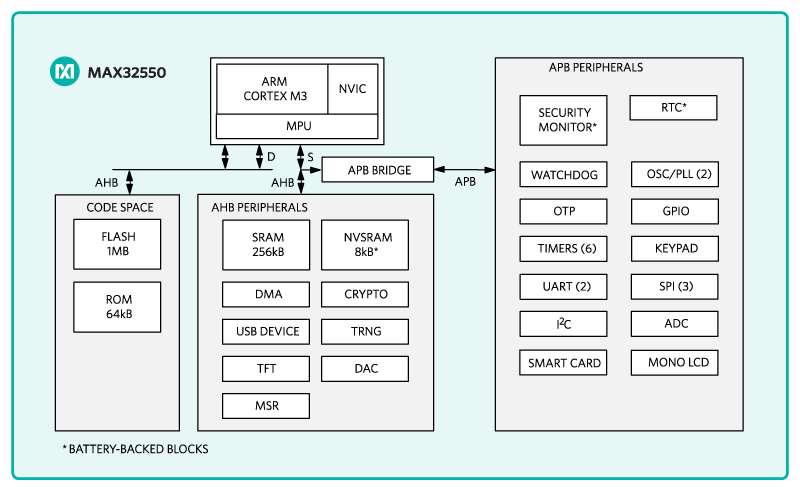

本文引用地址://m.amcfsurvey.com/article/274480.htm现在的微控制器在其片内集成了越来越多的外设。通常来说,外设对微控制器高效的完成工作起着至关重要的作用。外设起着连接传感器、系统控制、数据通信、故障控制和计时等多种作用。传统方法是使用中断来与片内外设通信。这样的优势很明显,大大的节约CPU时间,使得软件不必循环检测外设状态,从而本质上提高了CPU的效率。即使如此,中断方式仍然有一些劣势,其中一个就是中断例程中的上下文切换要花费一些处理周期。对于现代的CPU架构来说,中断的上下文切换需要20-100个时钟周期。假设有一个简单的任务,它获取发来的SPI数据。如果SPI的速率是1Mbps,则SPI接收中断的频率可达125KHz.如果SPI中断处理需要25时钟周期(包括上下文切换),那对于20MIPS的CPU时间来说,仅处理SPI中断就需要花费15%的CPU时间。如果同时还有其他一系列中断,则意味着CPU必须处理巨大的任务。

使用中断方式的另一个劣势就是中断响应时间对关键系统事件的影响。某些中断源可能要求在触发后CPU必须立即响应。比如汽车的安全气囊、动力设备的急停等危机情况以及紧急情况的应用。所有这些都要求立即相应,或者立即关闭控制系统以防止发生永久性灾难事件。如果CPU需要首先完成其他的中断服务程序或者需要花费较长的时间进行上下文切换,结果将无法预知。

目前,已经有些半导体厂商开发了一些新的技术。这些技术用来取代传统的中断方式或者DMA方式,使用这类技术进行外设通信可以节省大量的CPU时间。

c语言相关文章:c语言教程

单片机相关文章:单片机教程

单片机相关文章:单片机视频教程

单片机相关文章:单片机工作原理

评论