PCI总线I/O时序波形观测及分析

PCI总线(Peripheral Component Interconnect)即外设部件互连,是一种新型的、同步的、高带宽的、独立于处理器的总线。从1992年创立规范到如今,PCI总线已成为了事实上计算机的标准总线。其所以能在各类总线中脱颖而出,是因为其具有传输速度快、支持无限猝发读写方式、支持并行工作方式、独立于处理器、提供4种规格、数据线和地址线采用了多路复用结构、支持即插即用功能等特点。本文重点介绍了PCI总线的写周期的时序波形的测量技术及分析方法,给出了时序波形的分析结果。

2 PCI总线的功能

2.1 连接到PCI总线上的设备

连接到PCI总线上的设备分为两类:

(1)主控设备(master):PCI支持多主控设备,主控设备可以控制总线、驱动地址、数据及控制信号;

(2)目标设备(target):不能启动总线操作,只能依赖于主控设备向他进行传递或从中读取数据。

2.2 有关PCI引脚信号

有关PCI引脚信号说明如下:

AD[31~0]:地址、数据信号复用线。PCI总线支持写猝发和读猝发。一个总线传输分为 一个地址传送阶段和一个或多个数据传送阶段。有效,表示地址传送阶段开始,此时AD[31~0]包含一个32位的物理地址,选中I/O的一个字节单元或主存的一个双字单元。接下来为数据传送阶段(IRTY和TRDY同时有效),此时AD[7~0]包含最低字节数据,AD[31~24]包含最高字节数据。

C/BE[3~0]:总线指令和字节允许信号的复用线。在地址传送阶段,C/BE[3~0]上传送的是4位编码的总线指令。在数据传送阶段,C/BE[3~0]用作字节允许标志,以决定数据线上的哪些字节数据为有效数据,C/BE[3~0]可依次对应于字节3,2,1,0。

FRAME:周期帧信号。由当前总线控制者产生,表示一个总线传输的开始和延续。FRAME从无效变为有效.表明总线传输开始;保持有效,表明总线传输继续进行(1个或n个数据节拍正在继续);FRAME从有效变为无效,表明进入数据传输的最后一个数据传送阶段。

2.3 总线指令定义

在地址传送阶段,C/BE[3~0]线上送出总线指令的编码信息。总线指令用于对目标设备说明当前总线控制者正在进行的总线传输类型。表1给出了总线指令的定义。

I/O读:用于从一个被选中的I/O单元中读取数据。

I/O写:用于写数据到一个被选中的I/O单元中。

3 测量PCI总线的I/O写时序波形的技术及分析方法

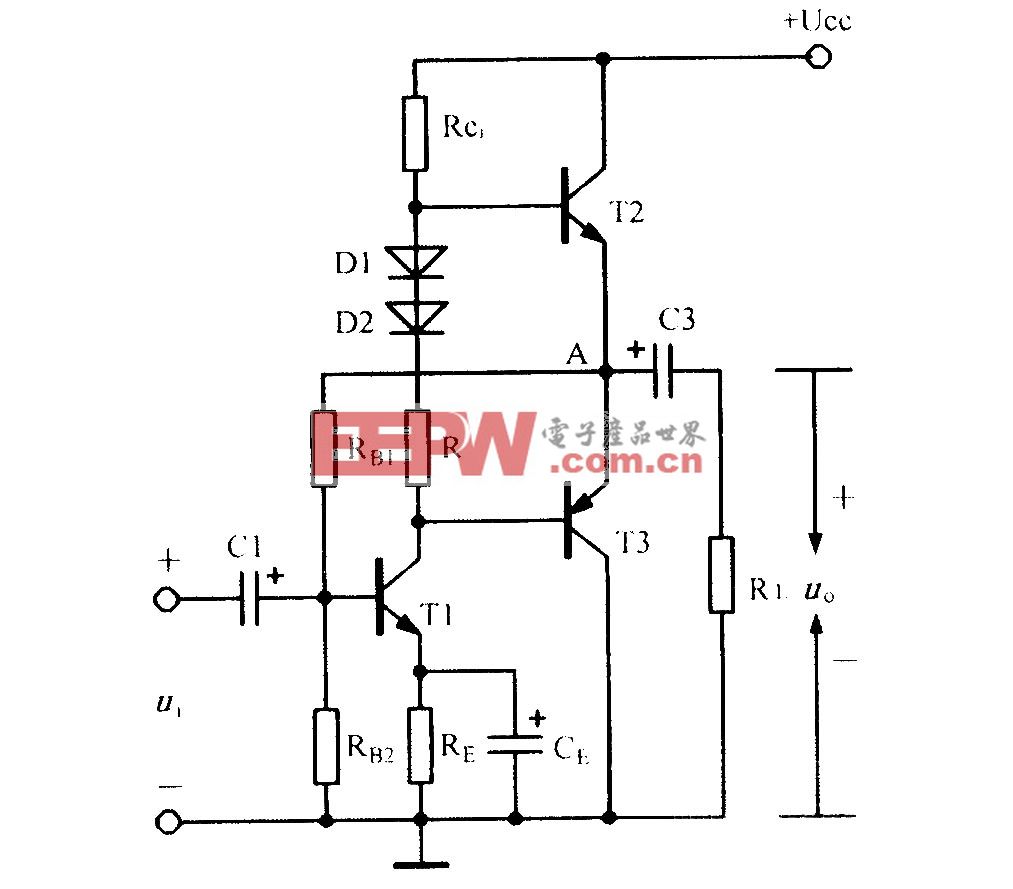

测量PCI总线的I/O写时序波形共分3个部分,如图1所示。

具体的实现测量的过程及分析方法介绍如下

3.1 编写测试程序

用汇编语言编写测试程序,该程序如下:

3.2 制作测试板

PCI波形采用厦门厦华三宝计算机有限公司状元一族主板,执行标准号:Q/FSl0938-1999。

取一块该PCI总线实验板,根据引脚说明,将要测试的各点用焊接的方法引出,并标明引脚名称,各测试点对应关系如下:

3.3 建立泰克示波器与PC机2通信连接

利用泰克TDS210型存储示波器的RS 232通信接口与pc机2相连,该PC机用来将示波器测出的波形转换为.CSV文件,过程如下:

PC机2与泰克示波器通信连接的操作步骤:

(1)TDS一210型存储示波器RS 232通信接口用专用电缆与PC机相连。

(2)打开存储示波器电源,启动PC机2。

(3)在PC机2窗口中点击Wavestar for Oscillose。

(4)点击Instrument manater(检测通信连接)→Responding(检测完成,关闭"

评论