基于OV6630图像传感器和DSP的图像采集系统设计

2 软件设计

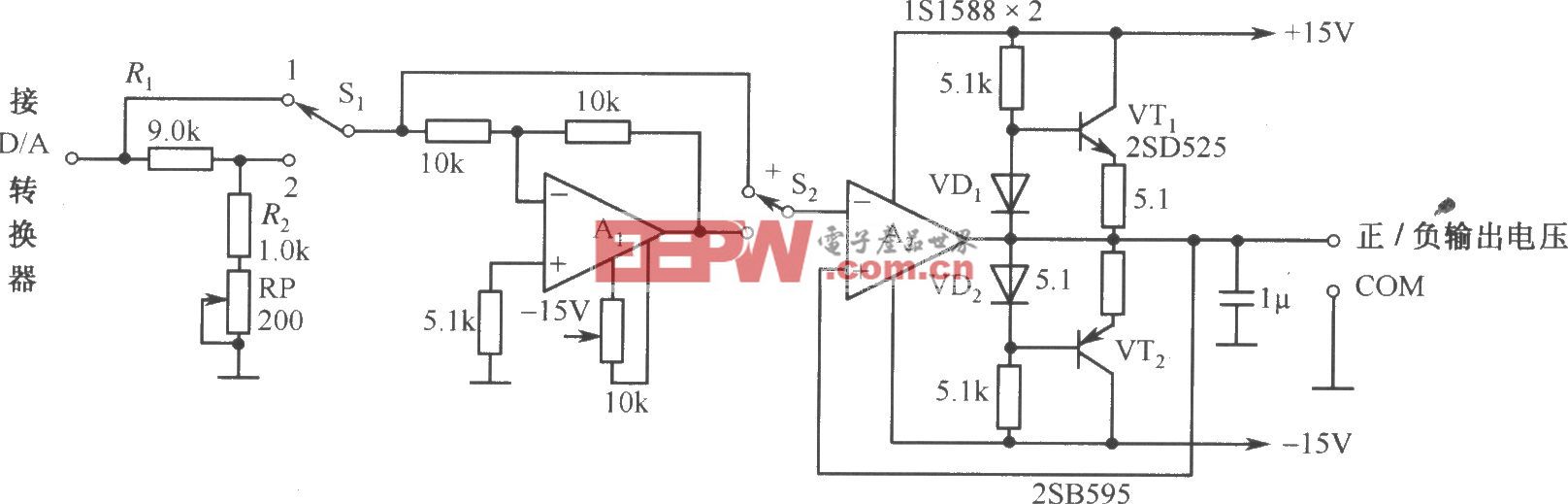

本文引用地址://m.amcfsurvey.com/article/85790.htm当系统配置完毕以后,便可以进行图像数据的采集与处理。在采集图像的过程中,最主要的工作是判别一帧图像数据的开始和结束的时刻。在仔细研究了OV6630输出的同步信号(VSYNC是垂直同步信号、HREF是水平同步信号、PCLK是输出数据同步信号)的基础上。笔者用VHDL语言实现了采集过程起始点的精确控制。图2所示为图像采集期间三个同步信号与数据信号的时序关系图。

图2中,每一个帧同步信号VSYNC周期包含288个水平同步信号HREF脉冲,而每一个HREF周期包含352个PCLK时钟脉冲,每一个PCLK时钟可输出一个RGB像素的视频数据。

通过监测系统中的垂直同步信号VSYNC的变化,即可得知新的一帧图像是否开始,一帧图像开始后,仅当HREF为高且PCLK输出下降沿时,才能输出一个有效的像素值。VSYNC的上升沿表示一帧新的图像的到来,下降沿则表示一帧图像数据采集开始(CMOS图像传感器是按列采集图像的)。HREF是水平同步信号,其上升沿表示一列图像数据的开始。PCLK是输出数据同步信号。只有当HREF为高电平时,才能开始有效的采集数据,PCLK下降沿的到来表明数据的产生,PCLK每出现一个下降沿可传输一位数据。HREF为高电平期间,共可传输352位数据。在一帧图像中,即VSYNC为低电平期间,HREF将出现288次高电平。而当下一个VSYNC信号的上升沿到来时,即表明分辨率为352×288的图像采集过程的结束。

CPLD控制的实现过程首先是按顺序检测VSYNC和CHSYNC信号是否有效,这时要注意防止毛刺信号的干扰。由于毛刺信号时间很短,设计时可采用设标志位的方法,即当检测到信号的有效沿后(对于VSYNC是上升沿,而对于CHSYNC是下降沿),可在等待一定时间后再次检测信号,看其是否仍然有效,如果有效,则说明信号是正确的。

由于系统中的像素数据是按PCLK时钟输出的,所以,可用来存储图像的SRAM使能信号CE。另外,其读写信号也是由CPLD产生的。因此,读信号RE只要在CPLD写操作中置“1”即可。由于在数据输出时,PCLK的上升沿信号比较稳定,而RAM可在WR上升沿将数据写入,因此,可以在HREF有效后(HREF=1)采用PCLK作为写信号RW。

由于图像像素点的个数已知,即数据个数已知,故在计数完毕后,CPLD将发出计数完毕信号。而DSP在接收到中止信号后,即可开始读取RAM中的数据,并对数据进行压缩和相应的处理,然后把数据放到LCD液晶屏的数据总线,最后将采集到的图像在液晶屏上显示出来。图3为图像采集系统的软件流程图。

3 结束语

本系统采用DSP和CPLD的综合方案来将图像的采集和数据的处理分而治之。实验结果表明,该系统图像清晰,且能满足实时显示的要求,可广泛应用在网络视频和工业自动监测等方面。

评论