- ST堆栈寄存器的作用,是出现中断或子程序调用时,保存断点处PC的值,以便中断或子程序结束时,能继续执行原程序。其原理图见2-10。图2-10ST堆栈寄存器原理图图中,信号STEN的作用是将...

- 关键字:ST堆栈寄存器

- OUT寄存器为输出端口寄存器,其原理图见图。图2-11寄存器OUT原理图图中,信号OUTEN作用是将数据总线DBUS上的数据送到输出端口寄存器OUT中。...

- 关键字:寄存器OUT原理

- 1、PIC16C62times;系列单片机的特点PIC16C62times;系列为RISC精简指令、哈佛结构总线、18个引脚的单片机。具有低功耗、高性能、全静态、35条指令极易编程的特点。OTP 片种的性价比极高。除了具备一般单片机的特点

- 关键字:寄存器二进制

- CAN总线(CAN.bus) 是一种串行多主站控制器局域网总线,其主要原理是把车辆上相关控制器都联系起来,实现发动机控制器,变速箱控制器,ABS控制器,车身控制器,仪表及其它控制器的通信。CAN—bus系统除了使整车

- 关键字:数据采集行车记录仪设计寄存器

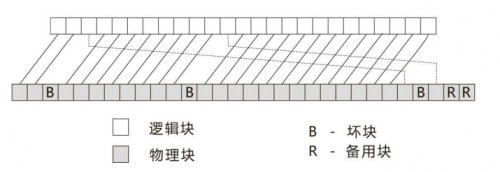

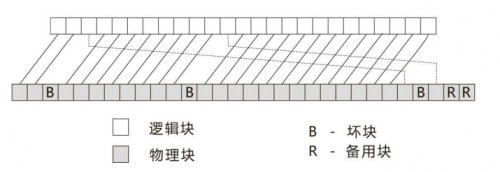

- 被广泛应用于手机、平板等数码设备中的Nand Flash由于工艺原因无法避免坏块的存在,但是我们可以凭借高科技变废为宝,将“坏块”进行有效的利用,从而满足我们的应用需求,让坏块不“坏”。 要想变废为宝,有效利用坏块。我们首先要弄明白什么是“坏块”,做到知己知彼,才能为我所用。坏块的特点是当编程或者擦除这个块时,不能将某些位拉高,从而造成编程和块擦除操作时的错误,这种错误可以通过状态寄存器的值反映出来。这些无效块无法确定编程时

- 关键字:Nand Flash寄存器

- 通用异步收发器(UART)是将数据从一个系统发送到另一个系统的最简单方法。UART通常集成在微控制器中,而且很多现代的IC都包含一个也可以同步通信的UART,称为通用同步/异步收发器(USART)。UART除了在系统中被广泛使用

- 关键字:UART通用异步收发器寄存器

- CMOS图像传感器是近年来发展最为快速的新型固态图像传感器,它利用其自身的工艺和集成的特点将光电成像阵列与信号模拟放大和数字图像处理电路集成于单芯片内,与CCD图像传感器相比,具有体积小、功耗低、控制简单、

- 关键字:CMOS调试系统接口DSP寄存器

- 基于实现简单高效地产生MSK调制信号的目的,文中系统性地阐述了AD9854的工作原理、机制,探讨了采用AD9854产生MSK 调制信号相比传统方法的优越性。同时详细介绍了通过FPGA配置AD9854的方法,描述了硬件平台的搭建并且列出了所有需配置寄存器列表。

- 关键字:AD9854MSKFPGA硬件平台寄存器

- 最近一直在研究信道编码,发现在信道编码里面有一个电路比较重要也比较有趣,那就是线性反馈移位寄存器 LFSR ,相信大家对 LFSR 电路也不陌生了,

- 关键字:LFSRCRC寄存器

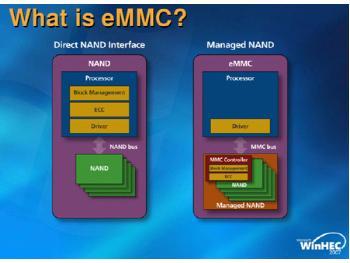

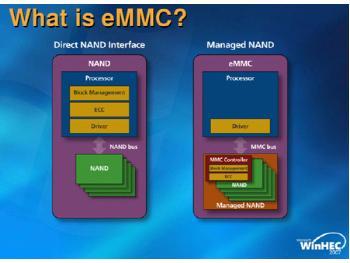

- eMMC芯片由NandFlash、控制器和标准接口组成,在应用上,和NandFlash比较,由于控制器的存在,不必考虑ECC和坏块管理策略,所以eMMC的应用比较简单。但是,eMMC烧写只需要把数据烧进去就可以了吗?为什么数据写进去了,系统还是跑不起来? eMMC自诞生以来,就受到各行各业的追棒,如今,已成为存储行业的主流,特别是手机和平板。美国的IHS iSuppli预测到2018年全球的eMMC出货量达到2200Milion。 图

- 关键字:eMMC寄存器

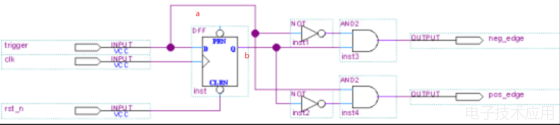

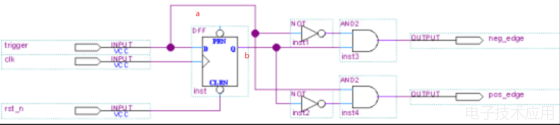

- 1、所谓边沿检测,就是检测输入信号或FPGA内部逻辑信号电平的跳变,即实现上升沿或下降沿的检测,捕获到以后以此用作使能信号(简单可理解为:一旦检测到这个信号,则发生什么什么),来作为时序逻辑的触发信号。总之,在基础中,这个还是很重要的,在后面的串口和SPI接口中都要用到。 (一)、一级寄存器 从一级寄存器中很好理解下降沿和上升沿的检测:a和b都是从trigger来的(三者一样),只是b比a在时间上迟了一个寄存器的时间。现在假设0时刻到了,trigger到

- 关键字:边沿检测寄存器

- 很多人肯定很疑惑,在嵌入式开发中,为什么写c代码,就能够控制硬件。这一切是怎么发生的了,下面我就给大家解剖一下,软件是怎么控制硬件的。 我们从控制8个led为例来说明: 从最简单的开始,如果使用硬件,控制8个led,最简单的方式是什么:直接接上开关。就是以下的图。通过开关控制led管脚输出不同的电平,就能控制led了。但是这个方法很不灵活,我们要手动的去拨动开关,才能改变led状态。 我们将上面电路改一下,把开关的地方换成寄存器,并加一些额外的电路,这样就

- 关键字:SOC寄存器

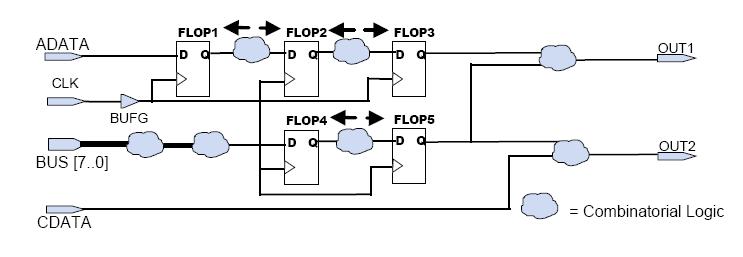

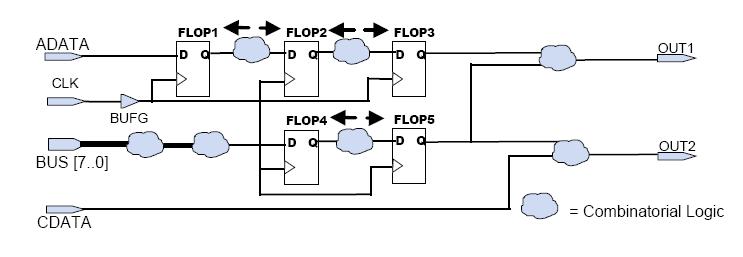

- 问题思考 单一的全局约束可以覆盖多延时路径 如果箭头是待约束路径,那么什么是路径终点呢? 所有的寄存器是否有一些共同点呢? 问题解答 什么是路径终点呢? ——FLOP1,FLOP2,FLOP3,FLOP4,FLOP5。 所有的寄存器是否有一些共同点呢? ——它们共享一个时钟信号,约束这个网络的时序可以同时覆盖约束这些相关寄存器间的延时路径。 周期约束 周期约束覆盖由参

- 关键字:ISE寄存器

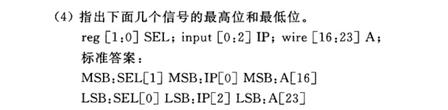

- 习题呢,来自夏雨闻老师的那本教材,就挑几个感觉自己做着有点难度的写写吧 这个题呢刚开始我是没看明白,记得书上只讲了我们习惯上的用法,这种用法我是没见过,问了下别人才知道,Verilog中一般是左高右低。第一个没问题,第二个,input [0:2] IP,习惯上我们这样写 input [2:0] IP,这里两个是等价的,即表示第0 .1 .2 三位。第三个,wire [16:23] A,也是,左高右低,表示第16.17.....22. 23位,左高右低就这样记就好了。

- 关键字:FPGA夏雨闻寄存器

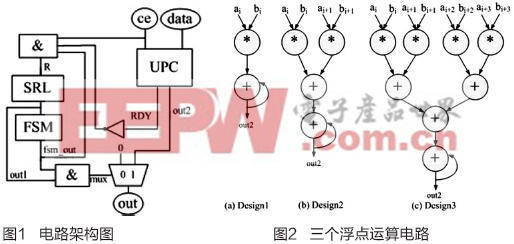

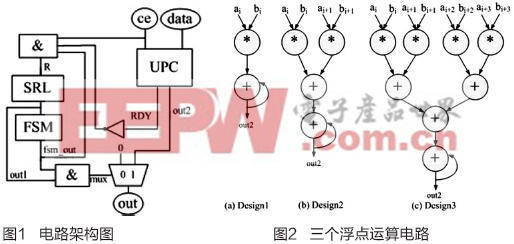

- 摘要:随着集成电路产业的迅速发展,集成电路设计的安全性越来越受重视,电路设计盗用等知识产权(IP)侵权行为严重损害了设计者和消费者的权益,阻碍了集成电路产业的发展。本文提出了一种有效保护IP核的方法,通过设计一个保护电路,控制功能电路运行结果的输出,在消费者未取得合法授权时,功能电路无法正常工作,从而达到了保护电路的目的。本文将该保护方法运用在实际的电路上,进行仿真并验证了该方法的有效性。 引言 随着片上系统SoC的迅速发展,IP复用的知识产权保护问题日益严重,危害了设计者和消费者的权益[

- 关键字:IP核FPGA寄存器IP固核RDY201412

寄存器介绍

寄存器定义 它是用来存放数据的一些小型存储区域,用来暂时存放参与运算的数据和运算结果。其实寄存器就是一种常用的时序逻辑电路,但这种时序逻辑电路只包含存储电路。寄存器的存储电路是由锁存器或触发器(一般用D触发器构成) 构成的,因为一个锁存器或触发器能存储1位二进制数,所以由N个锁存器或触发器可以构成N位寄存器。寄存器广泛地用于数字系统和数字计算机中。 寄存器分类 寄存器主要分并行寄存器和移位 [

查看详细]

关于我们-

广告服务-

企业会员服务-

网站地图-

联系我们-

征稿-

友情链接-

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473