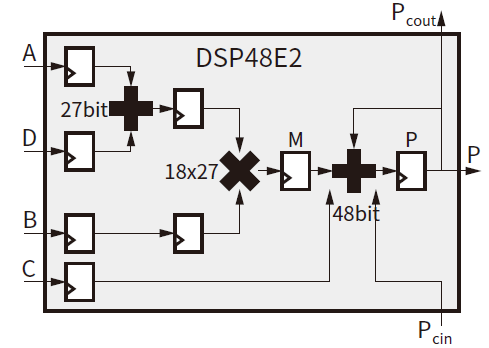

- 接上期//m.amcfsurvey.com/article/202009/418351.htm赛灵思 DSP 片上的 INT4 优化使用 DSP 硬件资源可实现乘法和累加 (MAC) 占用硬件资源较少。经优化后,DSP 能够在 16nm 或 28nm 器件上处理尽可能多的 MAC 运算。以 16nm 为例,赛灵思可编程器件中 UltraScale™ 架构的 DSP48E2 片就属于专用片[参考资料 11]。DSP48E2 片由一个 27x18 二进制补码乘法器和一个 48 位累加器构成。如图 3

- 关键字:赛灵思INT4卷积神经网络

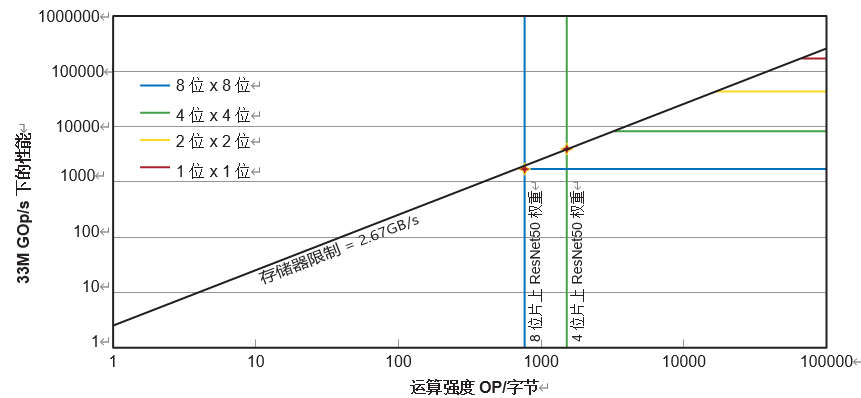

- 对于 AI 推断,在提供与浮点相媲美的精度的同时,INT8 的性能优于浮点。然而在资源有限的前提下,INT8 却不能满足性能要求,INT4 优化则是解决之道。通过 INT4 优化,与现有的 INT8 解决方案相比,赛灵思在实际硬件上可实现高达 77% 的性能提升。概要赛灵思在其硬件平台上提供 INT8 AI 推断加速器 — 深度学习处理器单元 (XDPU)。然而,在某些资源受限,要求高性能、低时延的场景(例如对资源、功耗敏感的边缘侧场景和低时延 ADAS 场景)中,为了实现比 INT8 更低的

- 关键字:赛灵思INT4卷积神经网络

int4介绍

您好,目前还没有人创建词条int4!

欢迎您创建该词条,阐述对int4的理解,并与今后在此搜索int4的朋友们分享。

创建词条

关于我们-

广告服务-

企业会员服务-

网站地图-

联系我们-

征稿-

友情链接-

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473