- 莱迪思半导体公司今天宣布推出印刷版的书“Power 2 You”, 针对电路板的电源管理功能,为设计人员提供150页的技术细节和设计考虑。作者是Srirama(“Shyam”) Chandra,他是电源管理领域被认可的专家,发表了多篇有关电源管理的文章。 电源管理的挑战 现代电路板使用CPU,FPGA和ASIC这样的超大规模集成电路,用它们实施主要的处理功能。这些超大规模集成电路需要多个安装在电路板上的电源,并以一个特定的序列打开,还要对故障

- 关键字:Lattice电源管理

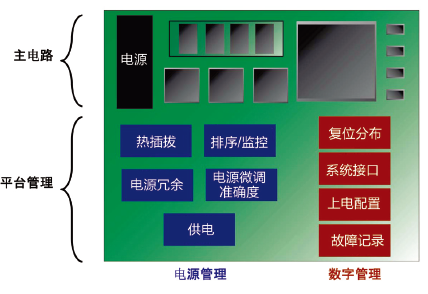

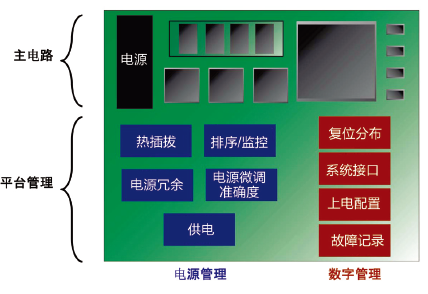

- 在FPGA行业,Lattice等中小公司为了避免和大型FPGA公司直接竞争,通常推出一些具有差异化的产品,例如在可编程混合信号芯片,使FPGA涉足传统模拟领地。 为改善电路板的电源与数字化管理,Lattice于10月12日发布了Platfrom Manager。该产品已是Lattice电源管理产品的第三代了—Lattice早在2003年推出了第一代产品—Power Manager,主要功能是排序和监控;2006年推出Power Manager II,增加了热插拔、电压测量、微调阈度。

- 关键字:LatticeFPGA201011

- 莱迪思半导体公司(NASDAQ: LSCC)与Helion今天宣布他们已经发布知识产权(IP)核用于视频安全和监控摄像机市场。针对LatticeXP2™、LatticeECP2M™和LatticeECP3™FPGA系列,Helion展示了其IONOS流水线型视频IP和Vesta评估平台。Helion Vesta评估平台是一个完全独立的平台,能够开发和实现针对摄像机系统的图像流水线技术,尤其是紧凑形式的视频安全应用,如网络IP和球型摄像机。 Helion的Ves

- 关键字:Lattice视频监控视频安全IP核

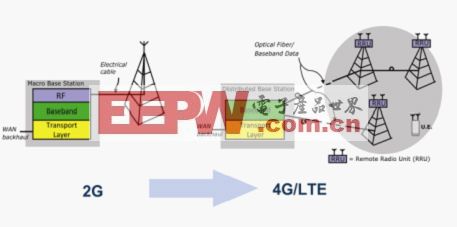

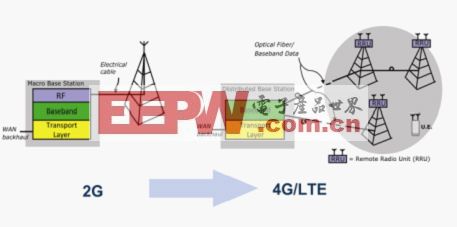

- 引言 随着人们订购无线服务数量的激增、各种服务类型的多样化,以及更低的便携式设备接入因特网的费用,使得对于增加基础设施容量的需求日益明显。3G智能手机、3G上网本和3G平板电脑是引发对于无线数据服务和基站容量的爆炸性需求的主要推动力。将性能叠加到现有的无线宽带设备,例如:HSPA+和EV-DO(即3G+),已经解决了一部分数据吞吐量的需要,但因为服务速度慢,无线服务供应商仍饱受用户指责,尤其是在大城市中,用户不满的情况更加严重。 无线运营商有向更高带宽服务发展的计划,如:LTE和LTE-A

- 关键字:LatticeFPGAJESD204A

- 电子产品世界,为电子工程师提供全面的电子产品信息和行业解决方案,是电子工程师的技术中心和交流中心,是电子产品的市场中心,EEPW 20年的品牌历史,是电子工程师的网络家园

- 关键字:Lattice中档FPGA多相滤波器

- SYNPLICITY和 LATTICE进一步加强合作,日前共同推出了面向 DSP 设计的高度优化的非专有 ESL 综合流程技术 Synplify DSP。Synplicity 的 Synplify® DSP 软件现可支持 LatticeECP2M 和 LatticeXP2 现场可编程门阵列 (FPGA) 器件,从而为航空航天、无线、电信及数字多媒体应用领域的 DSP 算法实施提供了功能强大的解决方案。 Lattice 公司的市场营销副总裁 Stan Kop

- 关键字:嵌入式系统单片机SYNPLICITYLATTICEDSPMCU和嵌入式微处理器

- Lattice半导体公司为高性能通讯和计算产品推出第二代零延时时钟发生器,它可产生20个时钟输出,每个输出的转换率都可以独立编程,提供标准输入输出和频率选择。ispClock5600A的锁相环(PLL)及分隔器系统可从参考输入综合多种时钟频率。 该发生器基于非易失系统内E2CMOS,与该公司第一代ispClock5600器件兼容,但增加了很多新功能,各种参数性能也有了显著改进。最大压控振荡器(VCO)工作频率已经提升到800MHz。它支持33.33-、100-、133.33-和50MHz时钟频率。输

- 关键字:Lattice可设计时钟网络

- 可编程逻辑器件融合CPLD+FPGA最佳特性 Lattice(莱迪思)半导体公司近日推出了新的MachXO可编程逻辑器件系列产品,Lattice称,这种新一代的跨越式可编程逻辑器件支持传统上由高密度的CPLD或者低容量的FPGA所实现的应用。 据Lattice现场应用支持副总裁Jock Tomlinson介绍,MachXO逻辑器件建立在低成本的130nm嵌入式Flash处理工艺上。它能够在单芯片中瞬时工作,这种特性对于许多CPLD应用来说是十分重要的。3.5ns的管脚至管脚的延时使得器件能够满足当代系统

- 关键字:Lattice(莱迪思)半导体公司

- 日本Lattice科技公司和法国Dassault系统公司日前(7/8)宣布合作,将共同开发3D资料压缩及传输技术和资料格式,并以成为全球业界标准为目标。Lattice是开发3维图形相关软体的公司,而Dassault则从事CAD相关软体开发,在此次合作中,Dassault将利用Lattice的3D资料减肥技术“XVL”,在Dassault的各种工具之间传输轻量3D资料

- 关键字:Lattice3D

- 莱迪思半导体公司不久前公布了ispLEVER 2.0 版__新一代的ispLEVER 设计工具套件,支持莱迪思新的ispXPGATM 和 ispXPLDTM产品系列,并集成了莱迪思 ORCA Foundry设计工具的特点和功能。在设计中通过使用类-LPM(Library of Parametrized Modules)宏,Module/IP Manager也可用来加速生成普通逻辑元件。ispLEVER floorplanner 提供ispXPGA 设计中逻辑的布局布线的控制。有色编码的图形用户接口帮助设计

- 关键字:Lattice

lattice介绍

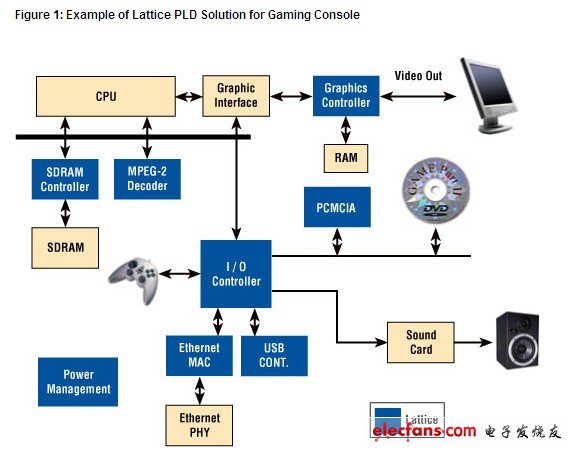

莱迪思(Lattice)半导体公司提供业界最广范围的现场可编程门阵列(FPGA)、可编程逻辑器件(PLD)及其相关软件,包括现场可编程系统芯片(FPSC)、复杂的可编程逻辑器件(CPLD),可编程混合信号产品(ispPAC?)和可编程数字互连器件(ispGDX?)。莱迪思还提供业界领先的SERDES产品。 FPGA和PLD是广泛使用的半导体元件,最终用户可以将其配置成特定的逻辑电路,从而缩短设 [

查看详细]

关于我们-

广告服务-

企业会员服务-

网站地图-

联系我们-

征稿-

友情链接-

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473