- 实验目的(1)熟悉和掌握FPGA开发流程和Lattice Diamond软件使用方法;(2)通过实验理解和掌握分频器原理;(3)学习用Verilog HDL行为级描述时序逻辑电路。实验任务设计一个任意整数分频器。实验原理时钟信号的处理是FPGA的特色之一,因此分频器也是FPGA设计中使用频率非常高的基本设计之一。一般在FPGA中都有集成的锁相环可以实现各种时钟的分频和倍频设计,但是通过语言设计进行时钟分频是最基本的训练,在对时钟要求不高的设计时也能节省锁相环资源。在本实验中我们将实现任意整数的分频器,分频

- 关键字:分频器FPGALattice DiamondVerilog HDL

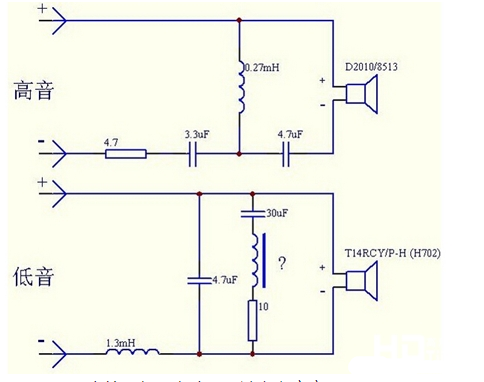

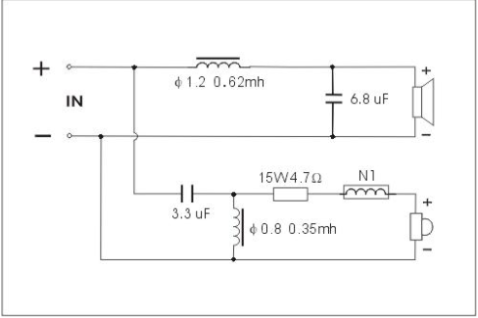

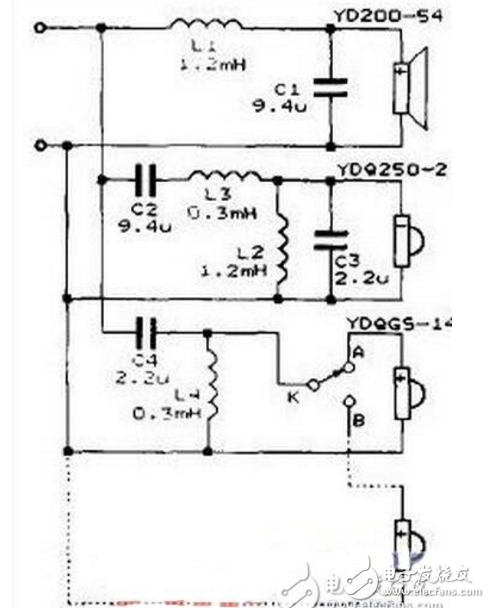

- 详解几款常用分频器及音箱分频器电路图-虽然中频单元的有效频响宽达800Hz~10kHz,L2、L3与C2、C 3组成的带通滤波器仅取其1.5~6kHz的一段频带,这也是它的黄金频段。L4、C4构成的高通滤波器将YDQG5-14的分频点定为6kHz,本单元的下限截止频率也取得较高,将更加轻松自如地在高频段发挥它的特长。

- 关键字:音箱分频器分频器

- verilog语言实现任意分频-原文出自:分频器是指使输出信号频率为输入信号频率整数分之一的电子电路。在许多电子设备中如电子钟、频率合成器等,需要各种不同频率的信号协同工作,常用的方法是以稳定度高的晶体振荡器为主振源,通过变换得到所需要的各种频率成分,分频器是一种主要变换手段。

- 关键字:verilog分频器电子电路

- 将50Hz或60Hz频率变成60分之1Hz频率的分频器

- 关键字:频率分频器

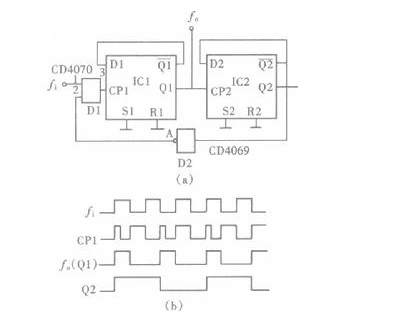

- 导读:分频器,顾名思义就是将输入频率进行分解,然后输出多路信号的装置,接下来我们就来学习一下分频器是如何分频的吧~~~ 1.分频器原理--简介 分频器是一种可以把输入信号的频率作出处理,使得输出信号的频率满足相关关系的电路,然后送到相应频段的扬声器中再进行重放。在高质量声音重放时,需要进行电子分频处理。锁相环频率合成器可利用分频器产生多个与基准参考频率有相同精度和稳定度的频率信号。分频器主要分为模拟分频器和数字分频器两大类。 2.分频器原理--分类 分频器主要可以分为以下两种:

- 关键字:分频器分频器原理

- 本文首先介绍了各种分频器的实现原理,并在FPGA开发平台上通过VHDL文本输入和原理图输入相结合的方式,编程给出了仿真结果。最后通过对各种分频的分析,利用层次化设计思想,综合设计出了一种基于FPGA的通用数控分频器,通过对可控端口的调节就能够实现不同倍数及占空比的分频器。 1.引言 分频器是数字系统中非常重要的模块之一,被广泛应用于各种控制电路中。在实际中,设计人员往往需要将一个标准的频率源通过分频技术以满足不同的需求。常见的分频形式主要有:偶数分频、奇数分频、半整数分频、小数分频、分数分

- 关键字:FPGA分频器

分频器介绍

分频器定义 分频器是音箱内的一种电路装置,用以将输入的音乐信号分离成高音、中音、低音等不同部分,然后分别送入相应的高、中、低音喇叭单元中重放。 分频器是指将不同频段的声音信号区分开来,分别给于放大,然后送到相应频段的扬声器中再进行重放。在高质量声音重放时,需要进行电子分频处理。 分频器作用 分频器是音箱中的“大脑”,对音质的好坏至关重要。功放输出的音乐讯号必须经过分频器 [

查看详细]

关于我们-

广告服务-

企业会员服务-

网站地图-

联系我们-

征稿-

友情链接-

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473