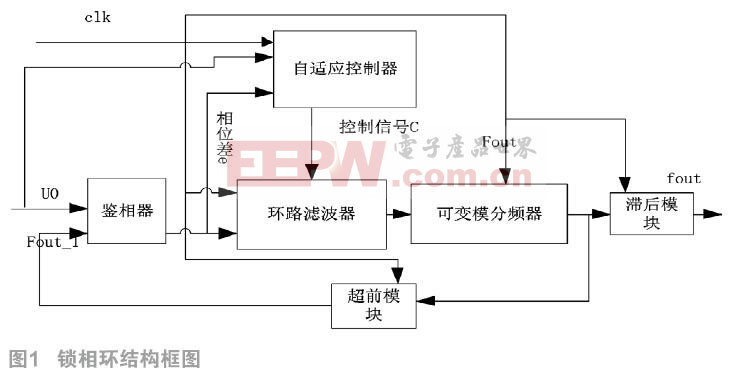

针对无线电能传输频率跟踪设计中传统锁相环电路设计复杂、跟踪速度慢、锁相频带窄和无超前滞后环节,单独模块设计修改繁琐等问题,对自变模全数字锁相环进行改进, 与传统的全数字锁相环相比,该锁相环采用可变模分频器,使得中心频率可变,锁相范围增大;通过前馈回路进行鉴频调频,提高了锁相速度;同时,其环路滤波器采用比例积分结构,使得锁相输出无静差且比例积分参数依据相位差自动进行调节;通过参数设置可调节输出信号的相位。应用modelsim进行仿真,并进行实物验证证实了该设计具有宽范围的锁相能力及快速精确的频率跟踪性能。