TPU神经网络加速器

1.1 EEP-TPU 张量处理器架构介绍

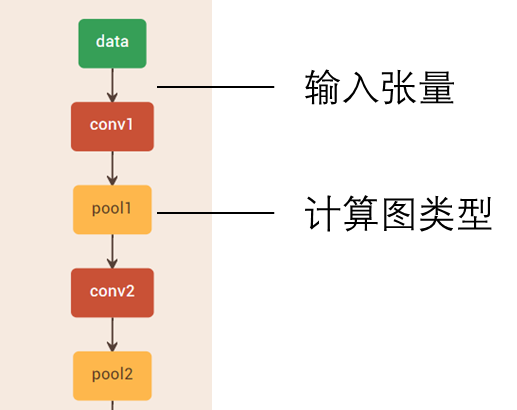

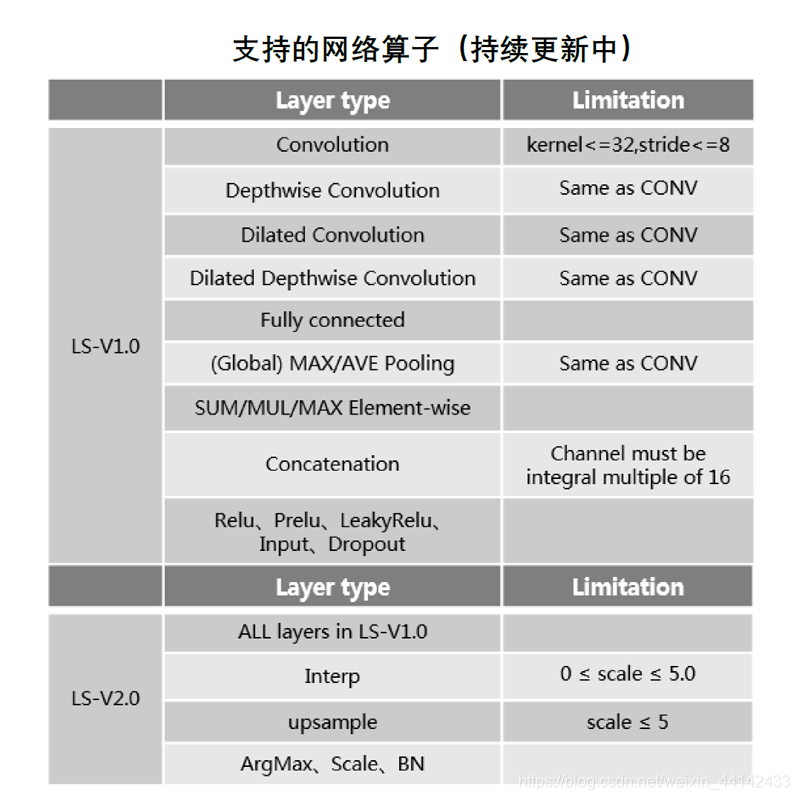

神经网络编程模型的本质是计算图模型,如下图所示,计算图的输入/输出是张量 数据,计算图的类型代表操作类型。因此,直观的,最适合于神经网络编程模型的计 算体系结构,是 Graph/Tensor 计算体系,其中,处理器的功能由计算图类型决定, 而数据则是计算图的输入/输出张量。

然而,计算图这一层级的粒度太粗,各类型间并没有太大的相关性,一个典型的 神经网络计算由 Convolution、Pooling、BN、Scale、RELU 等组成,它们之间的行 为差异巨大,如果处理器按照计算图操作的粒度去设计,这就意味着需要为每一个计 算图操作(或某几个)设计专门的计算硬件(正如 NVIDIA DLA 那样,NVDLA 为卷 积、池化和 BN 专门设计了不同的计算电路),这样的代价是巨大的,而且也不具备 可扩展性。

EEP-TPU 所采用的张量运算集用一种巧妙的方式解决了 Graph/Tensor 体系结构 中的核心问题:如何用一套标准、完善且最大粒度的操作( 粒度远远高于传统 CPU/GPU 的加、减、乘、除,同时也是各计算图的子集)来定义基础运算类型。

在张量运算集中,张量运算被划分为 1 维、2 维、3 维和 4 维四大种类,每个种类 又由各种不同类型的计算操作组成,从而形成一个完备的计算集合,通过这些张量运 算操作的组合,便能在相同硬件架构下,完成如卷积、DW 卷积、Pooling、Resize、 Relu 等计算图操作。

CPU、GPU、EEP-TPU 的处理器架构对比如下图所示:

相比于传统 CPU 的 Instruction/Data 和 GPU 的 Instruction/Thread 架构,EEP-

TPU 的 Graph/Tensor 架构有如下明显优势:

编程模型直观且简单。直接面向神经网络编程模型,使用计算图模型作为原始 输入,不存在模型转换和传统 CPU/GPU 软件并行编程的优化与匹配问题,在 合理的编译器分配下,便可最大化利用硬件资源。

无指令(计算图类型的切换,最终通过电路重构来实现,实际计算过程中并无 任何指令开销)。CPU 几十年架构演变的首要目标,就是增大指令执行效率, 减少指令调度和切换的开销。尽管 GPU 架构对指令调度的依赖较小,但其数 据计算仍然需要在指令的调度下统一工作。EEP-TPU 的无指令架构完全消除 了由指令引入的计算性能(由指令调度和切换引入)和计算资源(由指令控制 和存储引入)的开销。

内存带宽需求低。传统 CPU/GPU 架构是一种基于指令的计算体系,内存带宽 需求高,例如,一个 32 位加法操作,需要多次指令和数据的内存访问才能完 成。在 EEP-TPU 的 Graph/Tensor 架构下,每个数据只需从内存读出一次, 便可完成它生命周期内的所有计算操作,存储器访问频次降低到每个数据一次, 相比传统 CPU/GPU 完成相同工作要小得多,因此内存带宽的需求比传统 CPU/GPU 小得多。

片上缓存容量低。传统 CPU/GPU 架构需要引入多层级的存储结构来解决“存 储墙”问题。由于 EEP-TPU 无指令,且内存带宽需求低,因此只需一个小容量

的片上缓存便可满足计算过程中的数据缓存需求。

针对边缘、终端、传感器场景,通常一个 EEP-TPU Core 的算力就能满足绝大多

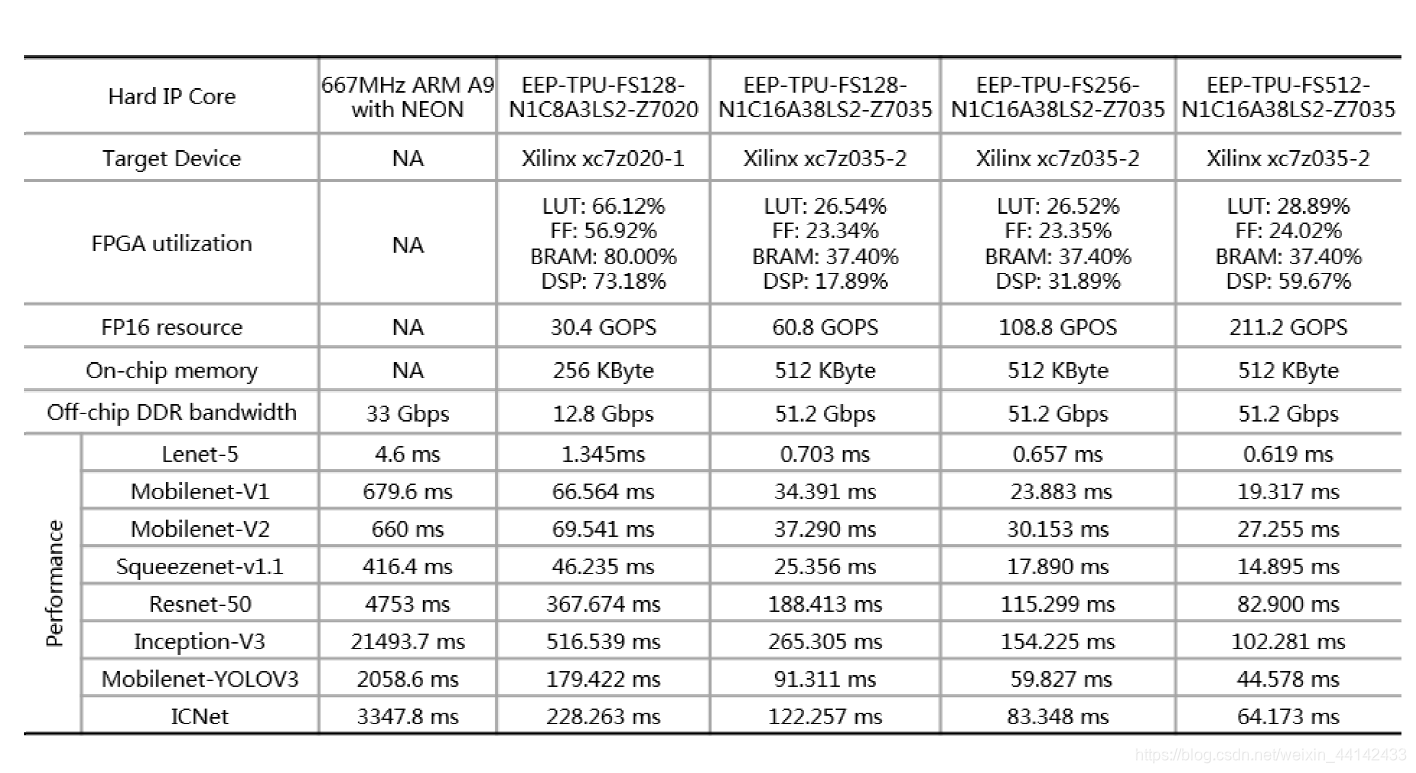

数应用的需求(28nm 工艺下最高算力为 2T FP16 FLOPS)。如果需要更高性能,则 可采用多核的方式实现性能扩展。特别的,在 Xilinx zynq 7020 上部署 EEP-TPU,算 力约为 0.03T FP16 FLOPS。在这样的算力水平下,已经可以实现最高 30FPS 的实时 目标检测任务(基于 YOLOV3)。而在多核架构下,算力可以轻松达到 32T FP16 FLOPS(英伟达 P100 算力为 18.7T FP16 FLOPS),如下图所示:

1.2 EEP-TPU 神经网络处理器架构

1.1所介绍的张量处理器,从集成电路设计与集成电路工艺的角度出发,仍然采用与 CPU、GPU、DSP 等传统芯片几乎相同的计算内核:乘法器电路。尽管体系结构的优化 可以使得乘法器计算内核的使用效率增加,但其仍然无法摆脱乘法器单元所带来的“性能 天花板”。神经网络处理器就是为了突破这种限制而产生的全新电路结构。

简单来讲,神经网络处理器就是希望使用全新的模拟电路形态的乘法器来代替传 统的数字电路形态的乘法器,并且把乘法器的计算单元与存储单元进行叠加,实现存 储与计算的一体化,从而达到 1~2 个数量级的性能提升。

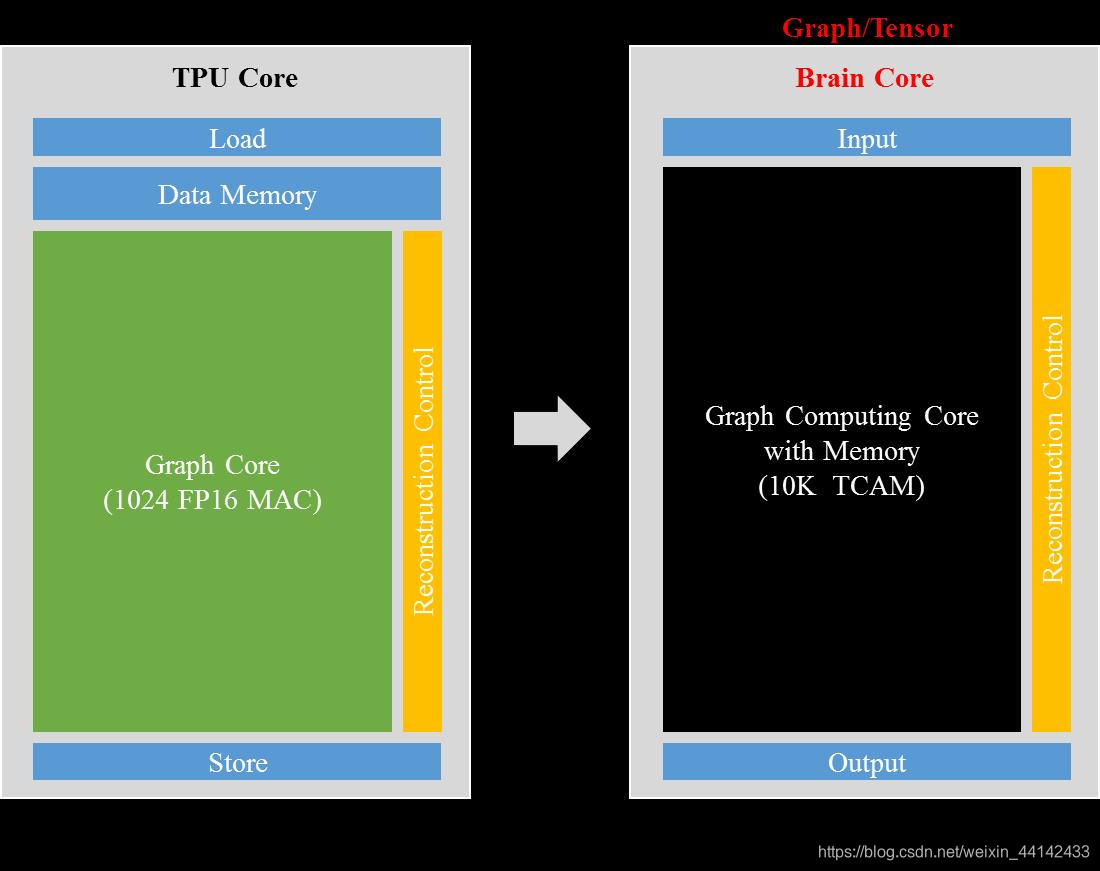

一种神经网络处理的架构演变如下图所示。

EEP-TPU 神经网络处理器属于全新的下一代产品,可以做到现有软件体系架构下

对张量处理器的全新升级与替换,目前仍处于验证阶段。

1.3 EEP-TPU 异构计算

在一个完整的人工智能芯片产品中,通常包含多种不同架构的处理器核心,最基本 的,至少包含一个 CPU 和一个 TPU。

对于一个包含 CPU 与 TPU 的人工智能系统来讲,CPU 与 TPU 可以完成相同的计 算任务,唯一的区别是能耗、时延、资源占用等性能的不同。在这里特别要注意的是, 尽管 TPU 是专门针对人工智能计算而设计的处理器,对于深度学习算法中的某种特定 计算类型来说,TPU 的计算并不一定有绝对的性能优势。例如, TPU 更擅长于处理数 据流计算类型的任务,而并不擅长仅通过坐标变换就能实现的控制类型的任务,而这 类控制类型的任务交由 CPU 实现具有更高的效率。

因此,由不同类型的处理器组成,并且各处理器发挥不同的优势共同完成某种计算, 成为了一个高效率人工智能计算系统的关键,这就是异构计算系统开发的初衷。

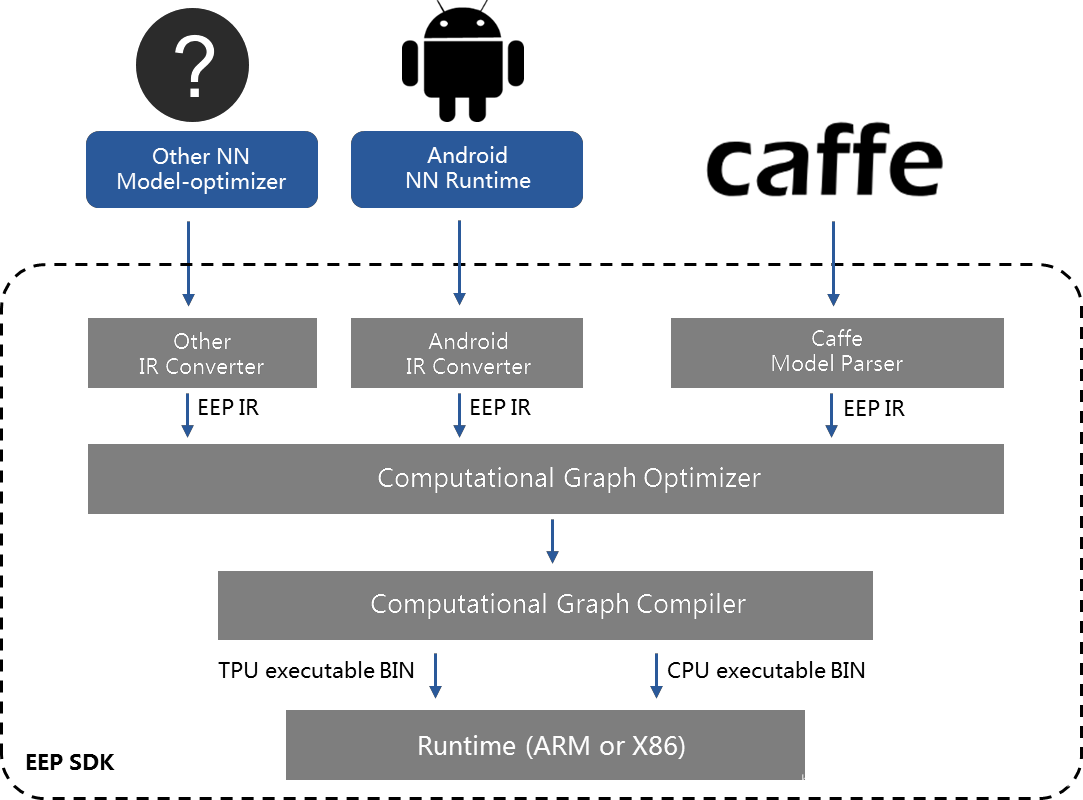

EEP-TPU 拥有一套完整的异构计算支撑体系。该支撑体系由编译器+异构计算框架

组成,可以支持由 CPU+TPU 组成的异构计算系统的高效计算。其中,编译器的作用 是分析来自用户输入的深度学习算法,并根据某种选择和规则,把深度学习算法进行 CPU 和 TPU 计算的切割,并分别进行优化与编译,最终生成 CPU 可执行文件和 TPU 可执行文件。EEP-TPU 编译器框图如下。

TPU 可执行文件和 CPU 可执行文件在实际工程中,将被打包成一个独立的 BIN 文 件,由运行在端末目标系统的异构加速框架读取并执行。

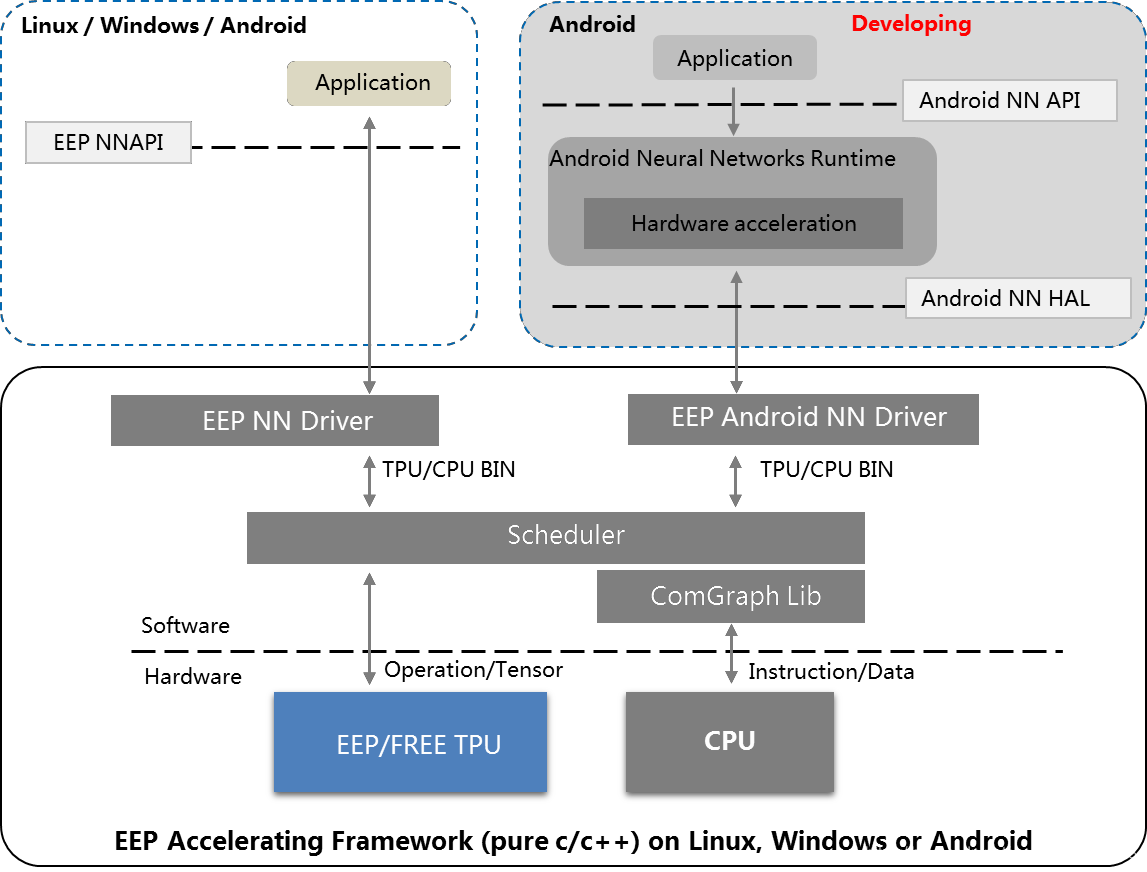

EEP-TPU 的异构计算框架是一套由 C/C++语言编写的,运行在目标操作系统之上 的底层软件系统,该软件系统读入来自编译器的可执行文件,并根据可执行文件的内 容,自动完成 CPU 计算与 TPU 计算的资源分配、任务调度、数据转换、数据传输等 工作,从而实现异构计算。

EEP-TPU 的异构计算框架封装了各种类型的的深度学习计算层,极端情况下,可 以不使用 TPU,仅使用 CPU 便可完成所有的深度学习计算(以极低的效率)。因此,

从用户的角度来看,该异构计算框架几乎可以承载所有类型层的计算,从而实现绝大

多数的深度学习算法,并通过使用 EEP-TPU,自适应的完成深度学习计算的高效加速。 在这过程中,用户对于该异构计算框架的使用几乎是无感的。

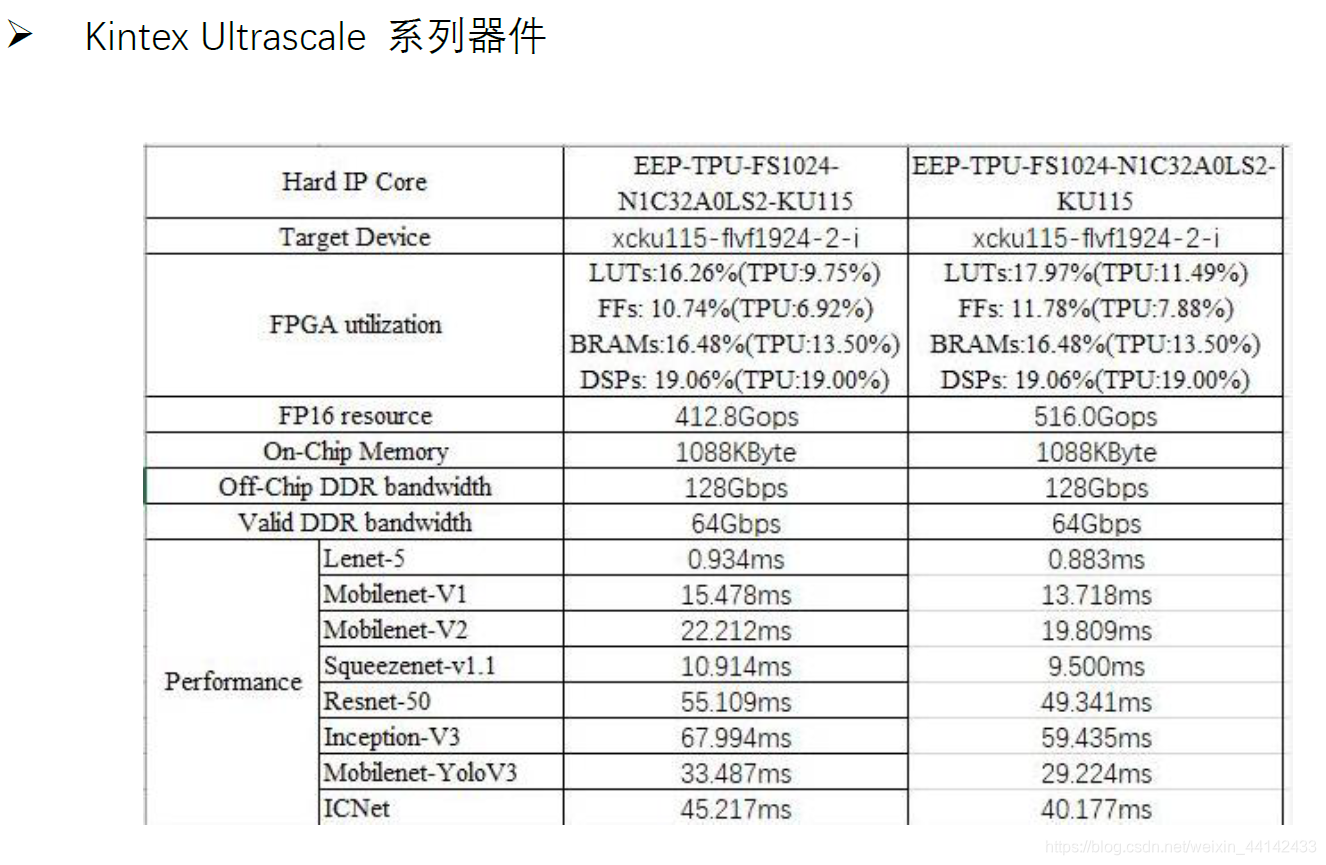

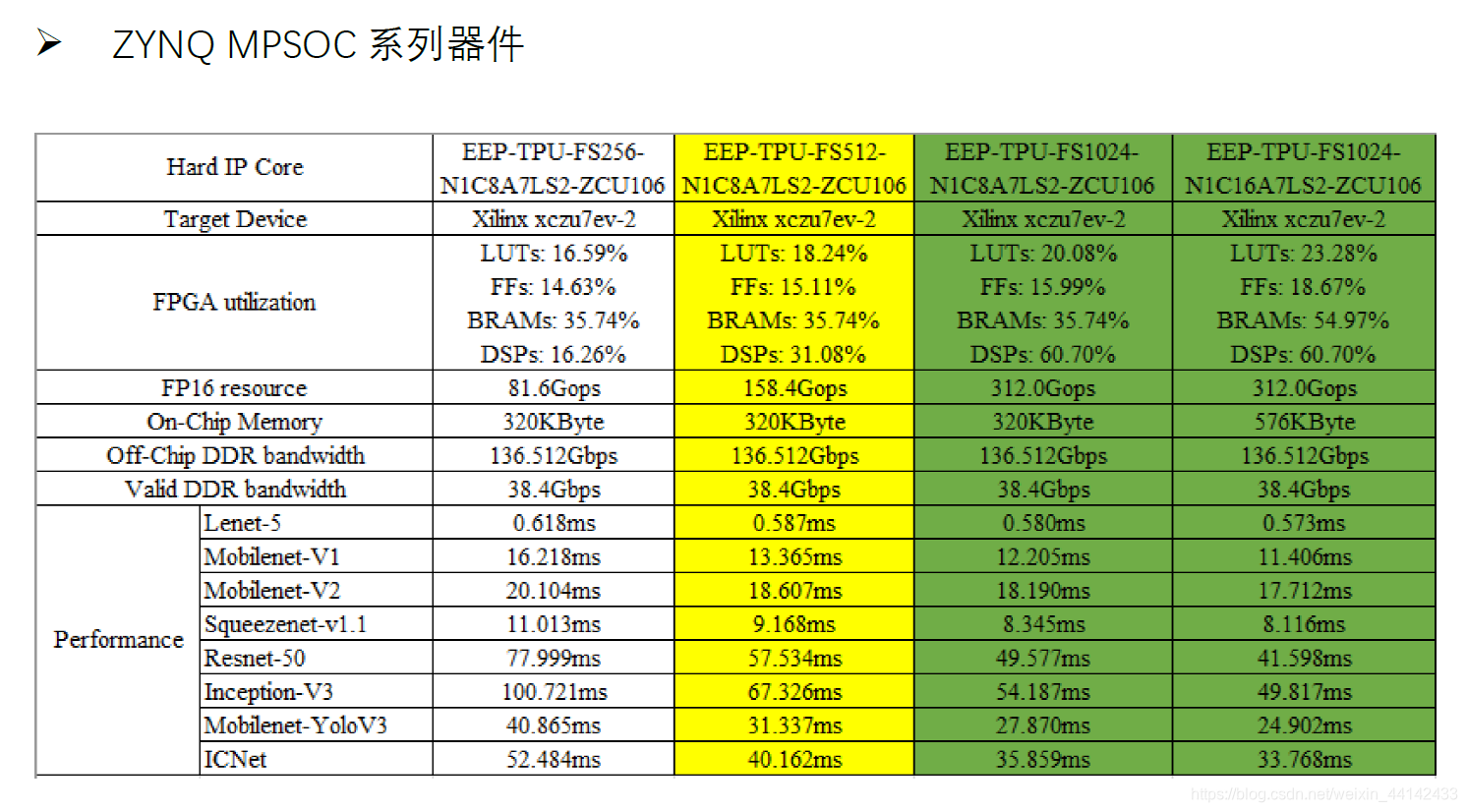

支持 TPU 神经网络加速器的 FPGA 平台

FACE-Z7:ZYNQ 7100 全可编程开发平台

FACE-ZU:ZYNQ UltraScale 多核心高性能计算平台

FACE-ZU:ZYNQ UltraScale 多核心高性能计算平台

FACE-V7:Virtex7 高性能可编程计算平台

FACE-V7:Virtex7 高性能可编程计算平台 FACE-KU:Kintex UltraScale 异构计算加速平台

FACE-KU:Kintex UltraScale 异构计算加速平台

FACE-VU13P大规模平台

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。