SI仿真封装模型与提取关注项

模型提取的准确性以及在不同场合的正确使用一直是SI仿真工作中的“应用核心”,因为它最能阐释什么是“Rubbish in,Rubbish out”。

为什么说模型是仿真的核心?

很久、很久以前,也就是【菊厂】刚成立Si部门之时,SI团队的某某问了IBM几个仿真问题,最后以国人的“客气”传统问了下对方需收多少费时“¥#%@¥#%OOXX……”,几个问题最后付了2万多美金(这是20多年前),我当时的直觉得就是“模型很值钱,知识很值钱”。

当习惯了SI仿真流程的越来越白痴化后,拿来就用成了理所当然的习惯。平时拿到一个SI仿真模型后,你是否曾想过:模型里的数据是怎么来的?你是否认真分析过里面的数据?

一般SI工程师拿到一个IBIS模型时,首选会使用IBIS Check类的软件看下是否有Error,对待出现的Warning很多人则直接选择了无视,我们实际做项目时还是应该把每个Warning的内容过一遍,但一些Warning的确认需要封装内部的知识支撑。

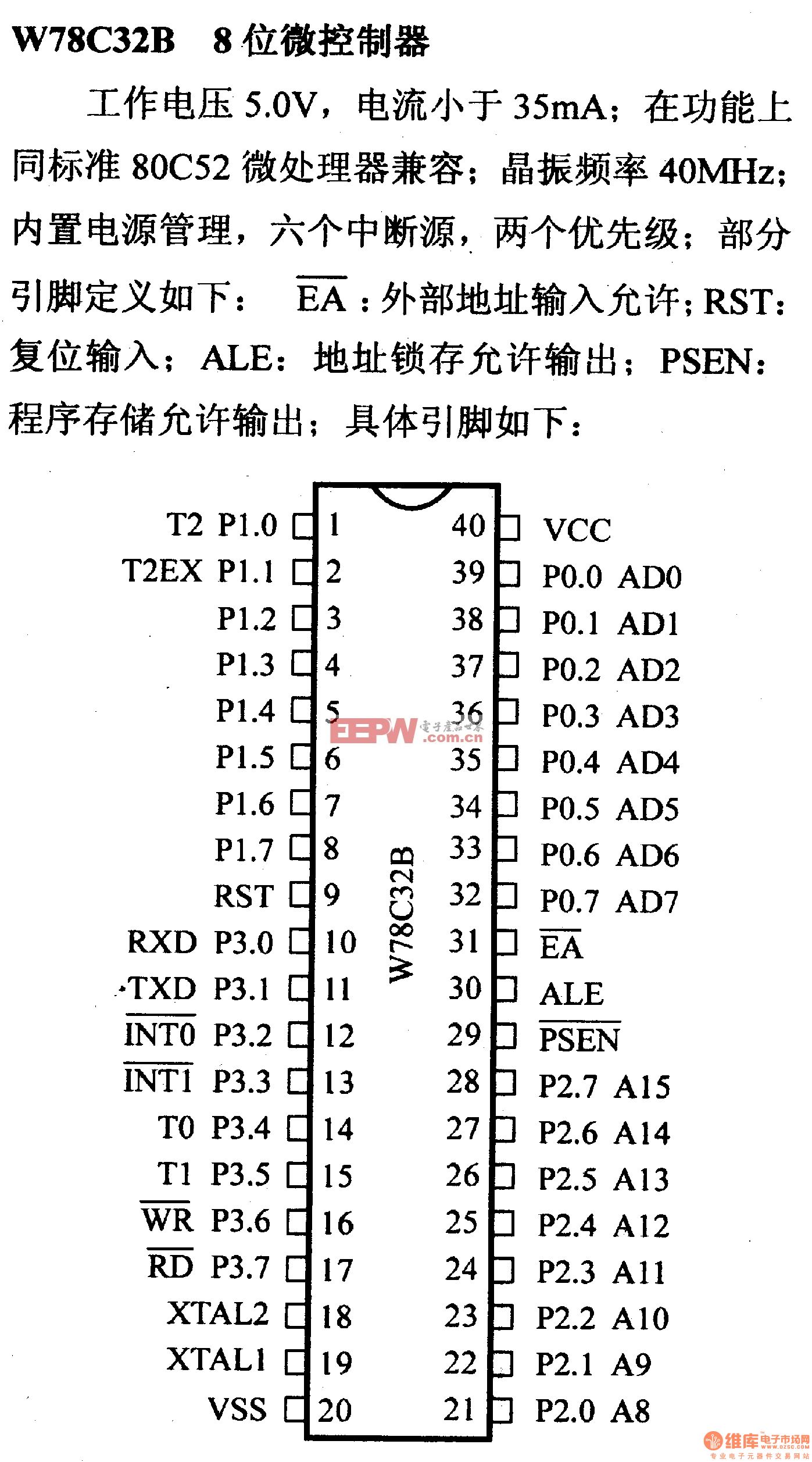

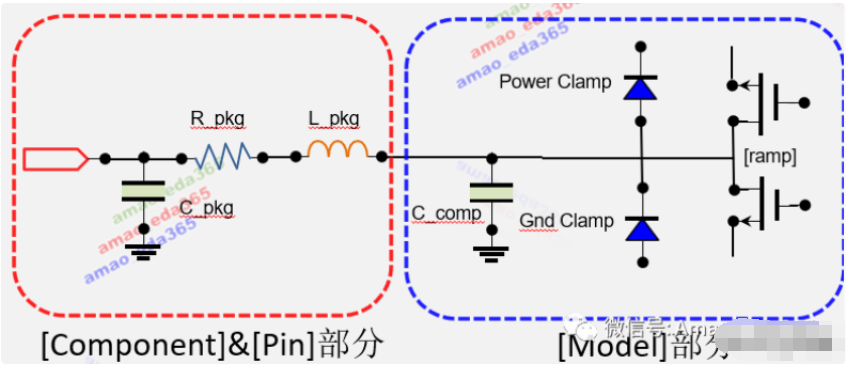

器件仿真模型主要由芯片封装+Buffer这2部分构成(当然,随着仿真的复杂化,后面会加入更多的其它内容),对Buffer的数据部分应保持它的原始性而不应进行手工的修改(每每想起以前有人把Buffer的数据修改以便使输出波形得到优化的手法就感到汗颜!)。

国内由于各方面的原因,芯片行业只有极少几家技术还不错,大环境一直没真正好起来,没有好实体企业支撑,广大工程屌丝相应就会缺少锻炼与成长的机会,就封装而言,很多人对封装的内部结构不了解,因而对封装模型文件中的数据分析起来就会感到吃力甚至糊里糊涂,以下的这些点在提取芯片封装模型时应要注意。

1

封装的结构

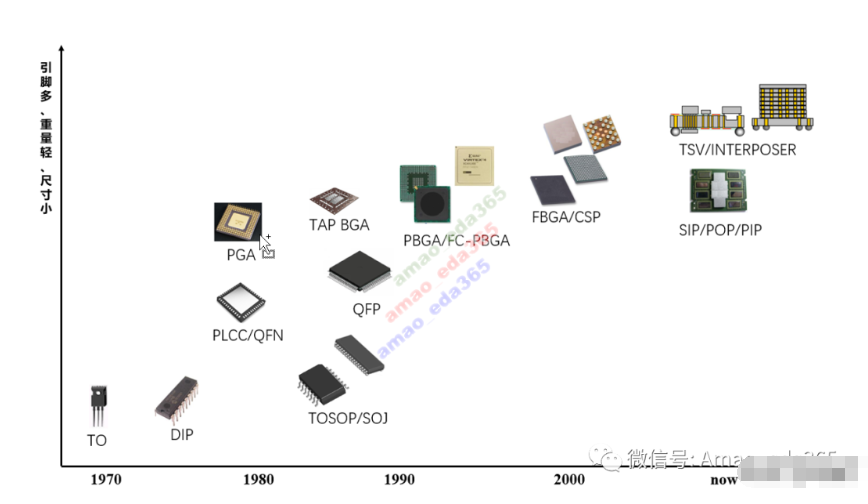

封装设计选型时一般都会尽量选用已有的封装模型,除非特别的需求会做一些局部的改动及优化,常见的装细分形式很多,如下图。但主体是WB与FC加工方式再结合的BGA与LEADFRAME的组合架构,随着技术的发展而衍生出TSV、Bar Die等等。

图2 封装发展趋势(基于Pin密度)

**图片摘自《芯片SIP封装与工程设计》

2

影响模型精度的因素

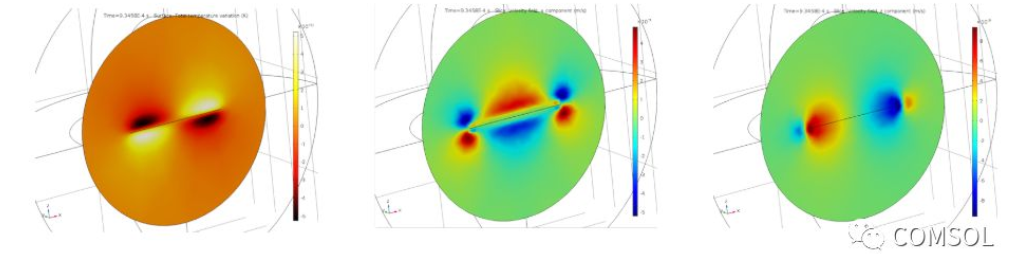

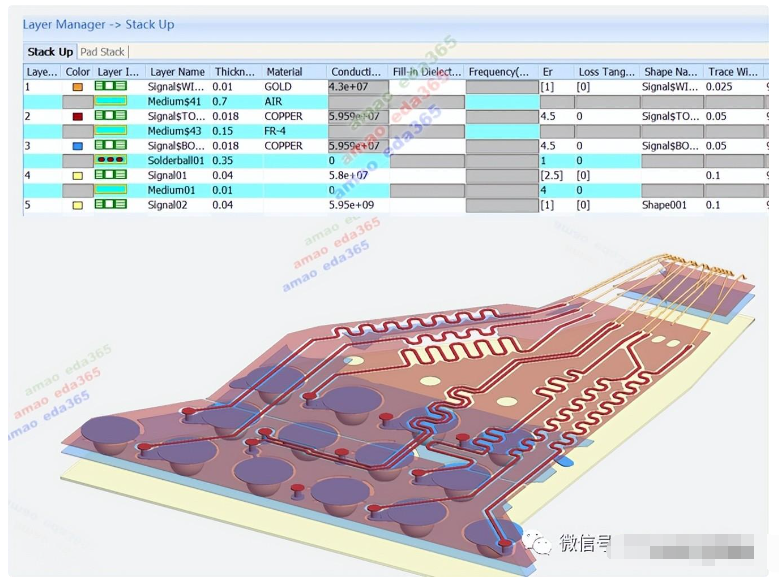

封装模型提取时,影响结果的因素很多,如:层叠与参数、地参考点选取、Wirebond外形结构、耦合精度设置等,这些在实际的提取时一般会作折衷的处理,模型提取不是越复杂就越好,需要有一个综合的考虑。

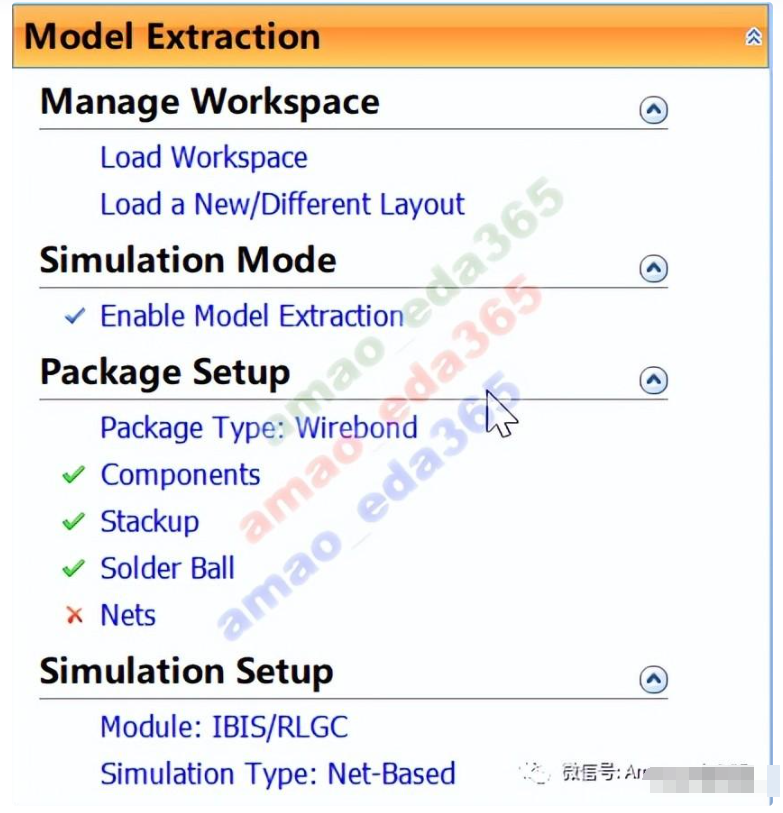

一般封装模型提取的流程如下(不同软件会有一定的差别),主要步骤设置有:层叠、Wirebond/Bump、焊盘及虚拟平面等,最后选上要提取的网络运行即可,如下图。过程非常简单,《芯片SIP封装与工程设计》书中已描述得太详细,在这里不作展开。

图3 封装模型提取流程

流程虽然简单,但是在设置如:Wirebond、材料的介电常数、参考地平面的选取等方面需要一定的工程经验,而不是随便填写一些不真实的数据,这些数据的选取及设置与项目经验有较大的关系,最佳的方式就是测试的回归验证。

3

模型仿真结果分析

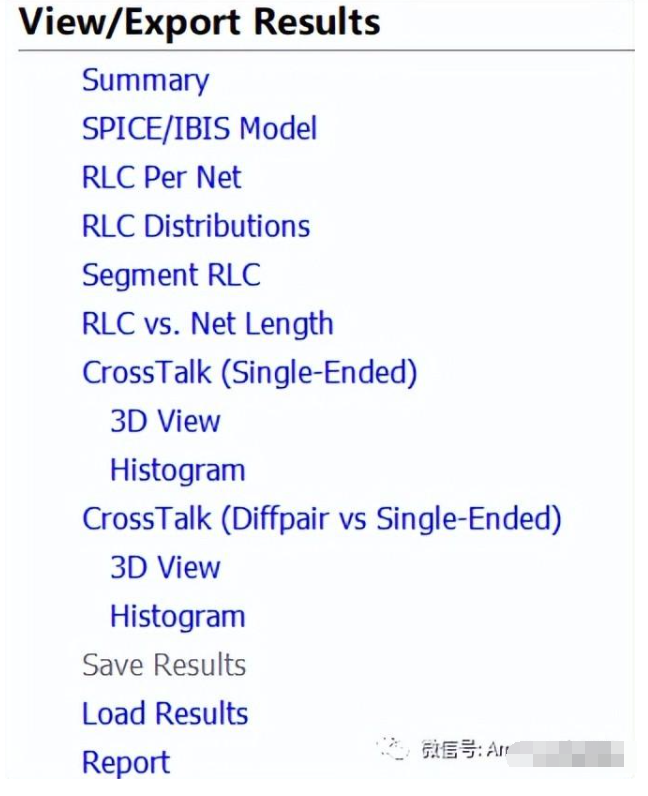

IBIS封装的电性参数有多种形式的网表输出,不同形式在不同工程应用场合会表现非常的高效,如:耦合的Pi型与T型网表、单线自身的RLC参数等等、如下图。

图5 仿真结果输出形式

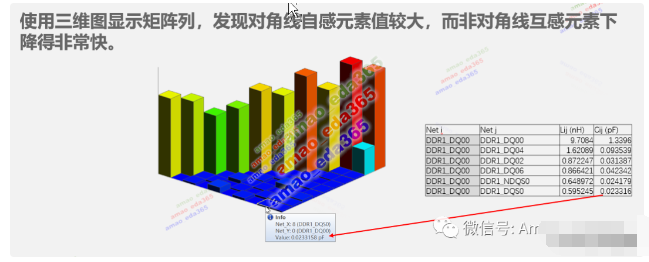

通过立体的输出结果则更便于检查,如下图互容与自容值的立体比较。

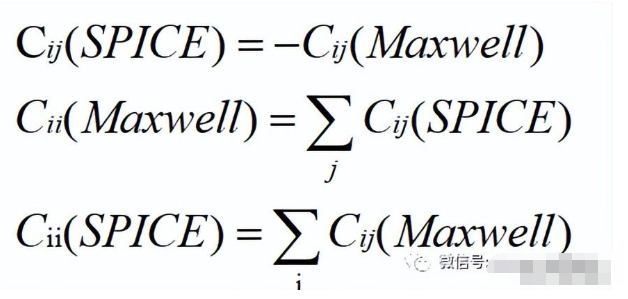

仿真输出的结果中,不同信号间的互容矩阵中的Spice矩阵与Maxwell矩阵需要特别注意,Maxwell认为是数学上的模型,而Spice通常认为是物理意义上的模型更易于理解,它们间的对应关如下式,因而拿到一个模型时如要引用它的自容与自感,需要弄清楚它属于哪类自容。

图7 Maxwell与SPICE电容矩阵关系

4

总结

对于SI仿真工作,不能简单按软件流程提取结果,更应花时间在模型的研究与提取上,从而使仿真的精度更有保障,随着芯片信号工作频率的提高,很多情况下只使用简单的RLC三个值的封装参数就会表现得捉襟见肘,使用PKG或S参数等带耦合性的模型可以使精度更高,当然如能获取封装设计文件自行提取则最为理想了。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。