3nm有多牛?什么时候投入量产?台积电告诉你

台积电3nm制程工艺将于今年进行试产,不出意外的话,2022年量产没有问题。在此基础上,业界对2nm工艺的进展投入了更多的关注,特别是台积电于2020下半年宣布2nm制程获得重大突破之后,人们对其更加期待了。与此同时,就在前不久,有19个欧盟成员国签署了一项联合声明,为加强欧洲开发下一代处理器和半导体的能力进行合作。其中包括逐渐向2nm制程节点发展的领先制造技术,此外,日本正在与台积电一起建立先进的芯片封装和测试工厂台湾半导体研究中心TSRI开始与日本产业技术总合研究所AIST合作,开发新型晶体管结构。日本媒体指出,这有助于制造2nm及更先进制程芯片,他们计划将合作成果应用在2024年后的新一代先进半导体当中。而2024年正是台积电2nm制程的量产年。

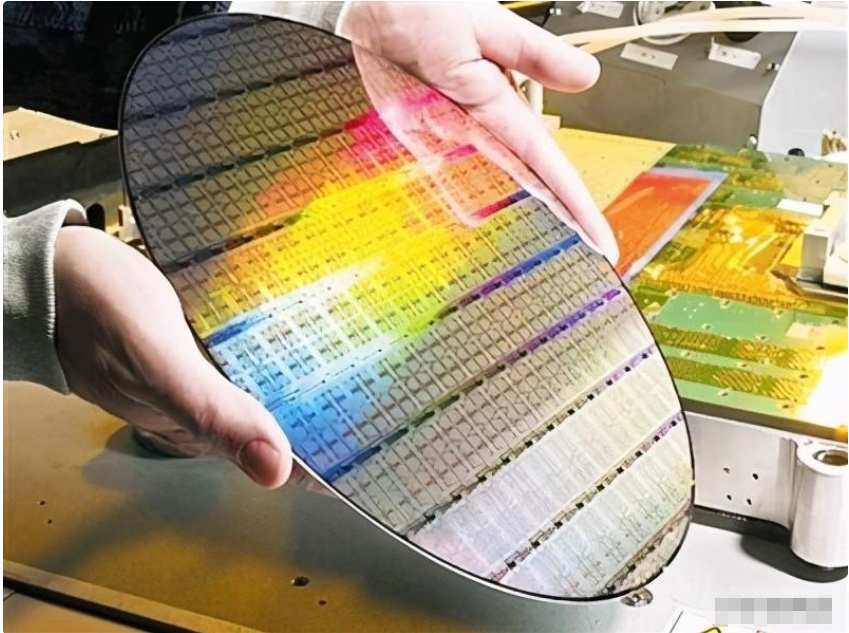

目前,距离2nm试产还有一段时间,各方面都在积极筹备当中,围绕着晶圆厂台积电,各大半导体设备供应商、材料工艺服务商、电子设计自动化EDA工具厂商,以及主要客户,都开始将越来越多的精力向2nm转移。目前来看,在3nm和2nm制程方面,台积电相对于三星的领先优势很明显,特别是2nm,还看不到来自于三星的权威信息。

2019年,台积电率先开始了2nm制程技术的研发工作,相应的技术开发的中心和芯片生产工厂主要设在台湾的新竹,同时还规划了4个超大型晶圆厂,主要用于2nm及更先进制程的研发和生产。台积电2019年成立了2nm专案研发团队,寻找可行路径进行开发,在考量成本、设备相容、技术成熟及效能表现等多项条件之后,决定采用以环绕栅极GAA制程为基础的多路桥接晶体管MBCFET架构,解决鳍式场效应晶体管FinFET因制程微缩产生电流控制漏电的物理极限问题。MBCFET和FinFET有相同的理念,不同之处在于环绕栅极GAA的栅极对沟道的四面包裹,源极和漏极不再和基底接触。根据设计的不同,环绕栅极GAA也有不同的形态,目前比较主流的四个技术是纳米线多路桥接晶体管、六角形截面纳米线、纳米环。

与台积电一样,三星对外介绍的环绕栅极GAA技术也是多路桥接晶体管MBCFET。不过,三星在3nm节点处就使用了环绕栅极GAA,而台积电3nm使用的依然是FinFET工艺。按照台积电给出的2nm工艺指标,金属单元高度和3nm一样,维持在5x,同时晶体管栅极间距缩小到30nm,金属间距缩小到20nm,相比于3nm都小了23%。按照规划,台积电有望在2023年中期进入2nm工艺试生产阶段,并于一年后开始批量生产。

2020年9月,据台湾媒体报道,台积电2nm工艺取得重大突破,研发进度超前,业界看好其2023年下半年风险试产良率就可以达到90%。目前,除了晶圆厂建设、台积电2nm人才安排和培育方面的工作也正在有条不紊地进行着。

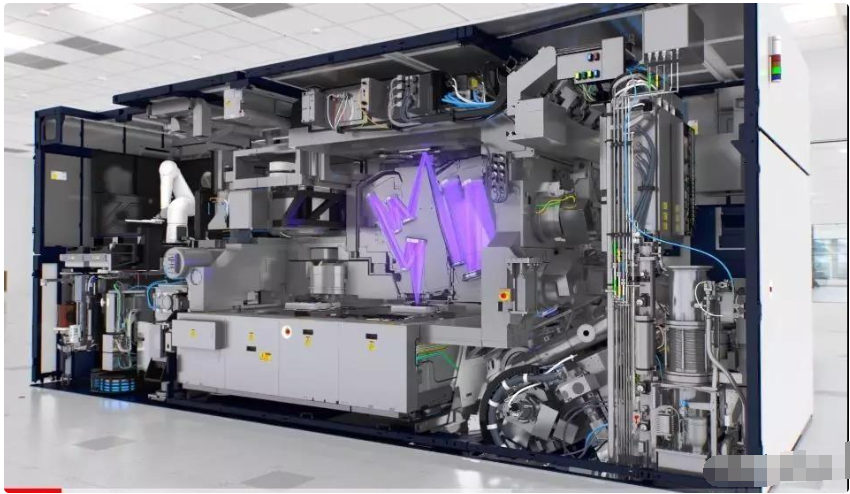

据报道,该公司在过去几个月提拔了4名员工,这些举措是为了让这些员工有更多的精力投入到2nm制造工艺的研究和开发当中,2nm制程平台研发部的高级总监,这个职位在此之前是不存在的,当该公司开始专注于2nm制程时,创造这个位置是很重要的。台积电对管理人员的学术要求很高,两位新提拔的副总经理都有博士学位。对于芯片制造来说,需要的设备很多,但就2nm这样高精尖的工艺来讲,极紫外EUV光刻机无疑是最为关键的。有统计显示,台积电2021年底将安装超50台EUV光刻机对于台积电先进制程所需的EUV设备,有日本专家做过推理和分析:在EUV层数方面7nm+为5层,5nm为15层,3nm为32层,2nm将达45层。因此,到2022年,当3nm大规模生产、2nm准备试产,需要的新EUV光刻机数量预计为57台。2023年,当3nm生产规模扩大、2nm开始风险生产时,所需新EUV光刻机数达到58台;到2024年,启动2nm的大规模生产,2025年生产规模扩大,到时所需新EUV光刻机数预计为62台。尽管现在EUV也将被用于内存芯片颗粒制造DRAM,但采用先进制程的逻辑芯片仍是主要需求方,高数值孔径High NA EUV光刻系统将始于2nm制程节点,其量产时间预估将是2025-2026年。

据悉,ASML将在2022年完成第1台高数值孔径EUV光刻机系统的验证,并计划在2023年交付给客户,主要就是台积电。对于极紫外EUV技术,台积电表示,要减少光刻机的掩膜缺陷及制程堆叠误差,并降低整体成本。今年在2nm及更先进制程上,将着重于改善极紫外光技术的品质与成本。之前有消息称,台积电正在筹集更多的资金,为的是向ASML购买更多、更先进制程的EUV光刻机,而这些都是为了新制程做准备。对于2nm和更先进制程工艺来说,EUV光刻机的重要性越来越高,但是EUV设备的产量依然是一大难题,而且其能耗也很高。

在不久前举办的线上活动中,欧洲微电子研究中心IMEC首席执行官表示,在与ASML公司的合作下,更加先进的光刻机已经取得了进展,欧洲微电子研究中心的目标是将下一代高分辨率EUV光刻技术高数值孔径EUV光刻技术商业化,由于此前的光刻机竞争对手早已经陆续退出市场,使得ASML把握着全球主要的先进光刻机产能。近年来,欧洲微电子研究中心一直在与ASML研究新的EUV光刻机,目标是将工艺规模缩小到1nm及以下。目前,ASML已经完成了,NXE:5000系列的高数值孔径EUV曝光系统的基本设计,至于设备的商业化至少要等到2022年,而等到台积电和三星拿到设备,要到2023年了。

前不久,中国大陆中科院的研究人员宣布,已经突破了设计2nm芯片的瓶颈,成功地掌握了设计2nm芯片的技术,这样的发展进程虽然让人们欣喜,但其实还是存在着比较多的问题。虽然已经有了这方面的技术研究突破,但是没有EUV设备的话,是不能够实现生产的。这从一个侧面反应出了EUV光刻机的重要性,也正是因为如此,全世界有先进制程能力的晶圆厂都将注意力集中到了ASML身上。对于像2nm这样先进的制程工艺来说,互连技术的跟进是关键。

传统上,一般采用铜互连,但是,发展到2nm相应的电阻电容延迟问题非常突出,因为,行业正在积极寻找铜的替代方案。目前,面向2nm及更先进制程的新型互连技术主要包括,混合金属化或预填充,将不同的金属嵌套工艺与新材料相结合,以实现更小的互连和更少的延迟;半金属嵌套,使用减法蚀刻,实现微小的互连;超级通孔、石墨烯互连和其他技术这些都在研发中。以混合金属化为例,该工艺在互连中使用两种不同的金属,对于2nm来说,这很有意义,至少对一层来说是这样。与双金属嵌套相比,通孔电阻更低,可靠性会提高,同时可以保持互连中铜的低电阻率。

业界还一直探索在互连中使用钌材料作为衬垫,钌以改善铜的润湿性和填充间隙而闻名,虽然钌具有优异的铜润湿性,但它也有其他缺点,例如电迁移寿命较短,以及化学机械抛光等单元工艺挑战。这减少了行业中钌衬垫的使用,其它新的互连解决方案也会陆续出现,但它们可能要到2023/2024年的2nm量产时才会商用。

根据欧洲微电子研究中心的路线图,行业可以从今天的双金属嵌套工艺转移到下一代技术,称为2nm混合金属化。接下来将还会有半金属嵌套和其它方案,台积电在材料上的研究,也让2nm及更先进制程量产成为可能。据悉,台积电和台湾交大联手,开发出全球最薄,厚度只有0.7nm的超薄二维半导体材料绝缘体,可望借此进一步开发出2nm,甚至是1nm的晶体管通道。

新的制程工艺离不开电子设计自动化EDA工具的支持,2nm也不例外,业内两大电子设计自动化厂商也早有相应的布局,面对如此高精尖的制程工艺,楷登电子Cadence和新思科技Synopsys创建了全新的EDA工具堆栈,并开发全新的设计知识产权IP库。2nm制程要求芯片开发人员必须采用全新的设计规则和流程,并重新制作他们以前可能使用过的所有内容。就像在2014年至2015年转向FinFET结构一样,增加芯片设计成本的同时,采用GAAFET可能会再次增加设计成本。新思科技表示,自由技术顾问委员会LTAB和互连建模技术顾问委员会IMTAB批准了新的建模结构,用以解决工艺节点低至2nm的时序和寄生参数提取问题。

移动设备对超低功耗的要求以及各种制造挑战,需要新的方法来确保在检查和确认时达到最佳精度,同时支持设计工具针对最低功耗进行优化。此外,这些节点上的器件架构、掩模和成像技术促使工件必须通过互连工艺文件ITF中的新扩展来建模。新思科技还推出了电路设计与工艺协同优化DTCO设计方法学,用以整合各种先进工艺。据悉,电路设计与工艺协同优化已经帮助客户实现2nm工艺设计。不久前,台积电总裁表示,台积电制程每前进一个世代,客户的产品速度效能提升30%-40%,功耗可以降低20%-30%,这或许是该公司不断追求先进制程的关键所在。目前来看,台积电将在业内率先量产2nm制程芯片已无悬念。而作为其近些年的头号客户,苹果成为最先尝鲜2nm芯片的厂商,也在情理之中。

此外,2024年之后,高通、英伟达、AMD等都会成为其2nm技术的客户。目前,以台积电的2nm,研发进度来看,2024年正式量产没有问题,也有报道指出,台积电已经在研究2024年的2nm的iPhone处理器,并且已经开始研究1nm制程节点技术。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。