一文了解CPU是如何实现存储的

为了了解CPU如何获得其处理能力,让检查CPU的实际功能以及它与数据的接口方式。在数字电子学中,一切都由二进制“位”表示。它是两种可能状态的基本表示。一个位可以表示零或一,对或错、向上或向下、接通或断开、关闭或任何其他双向值。

在CPU中,“位”在物理上作为电压电平传输。如果我们将多个“位”组合在一起,我们现在可以表示离散状态的更多组合。例如,如果我们将八位组合在一起,我们形成所谓的字节。一个字节可以代表256个不同的状态,可以是用于表示数字。对于字节,可以表示0到255之间的任何数字。但是在CPU中,我们如何选择表示数据完全具有延展性。同一字节也可以代表-128到127之间的数字。该字节的其他表达可能是颜色或声音级别。当我们将多个字节组合在一起时,我们创建所谓的单词。单词以其位容量表示。创建处理器时,其要处理的本机字长构成其架构的核心。原始的Intel 4004处理器以4位字运行。这意味着通过CPU传输的数据会传入一次四位的大块。通过使用更大的字长,我们可以表示更多的离散状态因此数量更大。在所有表格中,数据可以带入CPU内部,其中最重要的是一个是指令。指令是数据的唯一位,它们被解码并由CPU作为操作执行。一个常见指令的示例是添加两个单词一起取值或从一个位置移动一个数据字记忆到另一个位置。

CPU支持的指令的完整列表称为它的指令集。每条指令的二进制表示形式,其机器通常为代码分配人类可读的表示形式被称为汇编语言。如果我们看大多数CPU的指令集,它们都倾向于专注于对数据执行数学或逻辑运算,测试条件或将其从一个位置移动到内存中的另一个位置。出于所有目的和目的,我们可以将CPU视为指令处理机。

他们通过以下三个基本步骤进行操作,获取,解码和执行。随着CPU设计的发展,这三个步骤变得更加复杂并实施了扩展此核心运营模式的技术。但是,为了充分欣赏这些进步,让我们先探索一下基本的CPU操作机制。

今天被称为“经典的精简指令集计算机”或[RISC]管道”,这种范例构成了第一个CPU的基础设计。在提取阶段,CPU加载它将执行的指令被执行。可以将CPU视为存在于信息气泡中。它从自身外部提取指令和数据,执行操作在自己的内部环境中,然后将数据返回。此数据通常存储在CPU外部的内存中,该内存称为随机存取存储器或[RAM]。软件指令和数据从以下位置加载到RAM中更多永久性资源。

当CPU加载一个数据字时,它通过请求RAM中某个位置的内容。这称为数据的地址。确定一次CPU可以处理的数据量通过其地址容量。例如,一个4位地址只能直接寻址16个数据位置。存在用于处理比CPU地址容量更多的数据的机制,但现在暂时忽略这些。数据来回移动到RAM的机制称为总线。CPU和RAM的每一位数据都有自己的通道,以容纳数据字和地址字。这些分别称为数据总线和地址总线。当CPU发出RAM访问请求时,将进行内存控制CPU的区域将存储字加载到地址总线解决它希望访问的地址。然后,它触发一条控制线,该信号线发出存储器读取请求。收到此请求后,RAM用内容填充数据总线所请求的内存位置。现在,CPU在总线上看到此数据。使用CPU将数据写入RAM的工作方式类似而是发布到数据总线。当RAM收到“写”信号时,数据内容总线被写入地址总线所指向的RAM位置。要提取的存储位置的地址存储在CPU中,在一种称为寄存器的机制中。寄存器是一个高速内部存储器字,它被用作寄存器。CPU操作的“记事本”。通常用作说明的临时数据存储但也可以分配给重要的CPU功能,例如跟踪正在RAM中访问的当前地址。由于它们是先天设计在CPU硬件中的,因此大多数只有少数几个寄存器。

它们的字长通常与CPU的本机体系结构耦合。一旦将一个内存字读入CPU,用于存储的寄存器该字的地址(称为程序计数器)将增加。在下一次提取时,它将按顺序检索下一条指令。从RAM访问数据通常是CPU操作的瓶颈。这是由于需要与组件接口与CPU物理距离较远。在较旧的CPU上,这并不是什么大问题,但是因为它们变得更快,内存访问的延迟成为一个关键问题。提取指令后,解码阶段便开始。在经典的RISC架构中,一个字的存储形式完整的说明。随着CPU的发展,这种方法变得更加复杂。

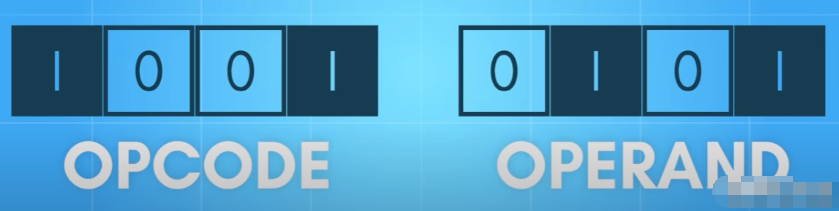

解码指令时,单词被分解为两个部分称为位域。这些称为操作码和操作数。操作码是代表特定字符的唯一的一系列CPU内的功能。操作码通常会指示CPU将数据移至寄存器,然后移至寄存器和存储器之间的数据,执行数学或逻辑功能在寄存器和分支上。当指令引起指令改变时发生分支程序计数器的地址。这将导致下一次获取在内存中的新位置处发生反对到下一个顺序地址。当确保“跳转”到新程序位置时,称为无条件分支。在其他情况下,可以进行测试以确定是否应该发生“跳跃”。这称为条件分支。触发这些条件的测试通常是数学上的,如果寄存器或内存位置小于或大于一个数字,或者为零或非零。分支允许程序做出决定,并且可以对CPU的功能至关重要。操作码有时需要数据来对其执行操作。指令的这一部分称为操作数。操作数是背负在指令上的位,用作数据。在某些指令中,操作数未指定其值自我,但包含要访问的内存中某个位置的地址。这在请求存储字的操作码中很常见加载到寄存器中。这被称为寻址,并且可以得到更多。

在现代CPU中很复杂。由于以下原因,寻址可能会导致性能下降。需要“离开” CPU,但是随着CPU设计的进步,这种情况得以缓解。一旦有了操作码和操作数,操作码就可以通过表格和电路的组合,然后由控制单元进行配置CPU的各个操作部分以执行该操作。在某些现代CPU中,解码阶段不是硬连线的,可以编程。这允许更改指令的解码方式以及CPU被配置为执行。在执行阶段,将触发现在配置的CPU这可能会在一个步骤或一系列步骤中发生取决于操作码。

CPU执行中最常用的部分之一是算术逻辑单元或ALU。该电路块旨在接收两个操作数,并且对它们执行基本算术或按位逻辑运算。然后将结果与相应的数学公式一起输出标志,例如结转,溢出或零结果。然后将ALU的输出发送到寄存器或位置根据操作码在内存中。假设一条指令要求将10加到寄存器中将结果放入该寄存器。

CPU的控制单元将加载立即值指令进入ALU,将寄存器的值加载到ALU中并连接ALU输出到寄存器。在执行触发器上,添加完成并输出加载到寄存器中。实际上,软件精简到配置循环在CPU中相互交互的多组电路。在CPU中,这三个阶段的操作连续不断地循环,使其工作通过指令的方式将计算机程序加载到内存中。将这台打环机粘合在一起是一个时钟。时钟是重复脉冲,用于同步CPU内部机械及其与外部组件的接口。CPU时钟速率是通过每秒的脉冲数或赫兹来衡量的。英特尔4004以740 KHz或每秒740,000脉冲的速度运行。现代CPU可以达到接近5GHz的时钟速率,或者每秒50亿个脉冲。

在较简单的CPU上,单个时钟会触发时钟的提前。获取,解码和执行阶段。随着CPU变得越来越复杂,这些阶段可能需要花费几个时间时钟周期完成。CPU的吞吐量,可以执行的指令量一秒钟确定它有多“快”。通过提高时钟频率,我们可以使处理器运行通过其阶段更快。但是,随着我们变得越来越快,我们遇到了一个新问题。时钟周期之间的周期必须留出足够的时间用于执行的每种可能的指令组合。如果在指令周期之前发生新的时钟脉冲完成,结果变得不可预测,并且程序失败。此外,增加时钟速率具有增加的副作用。功耗和CPU中的热量积聚导致文化绩效的下降。更快,更高效地运行CPU的战斗主导了它的整个存在。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。