基于S3C2440的LED背光源节电系统设计方案

引言

本文引用地址://m.amcfsurvey.com/article/148339.htm节能环保技术是当前世界所关注的焦点,在液晶显示模组中,背光源的功耗最高可占总功耗的50%以上。尤其在10in 以下显示产品如手机、PDA、MP3 等便携式设备中,基本采用电池供电,功耗问题尤为突出。为有效降低液晶显示器背光源的亮度,以达到节电目的,本文在ARM 开发平台上实现了一种基于直方图变换的背光源调光方法,实验证明,本文提出的方法在失真度为5%的情况下可实现背光节电约35%.

1 背光源调光方案

以TFT 液晶面板结构为例,包括背光、偏光片、液晶阵列、彩色滤光片等部分,人眼所感知的显示图像为上述各部分的综合效果。假设背光亮度归一化后设为b(为[0,1]区间实数),0 对应于背光关闭情况,1 对应于背光发光亮度最大情况。若光源为LED,则b 的调节可包括电流脉宽调制、电流幅度调节等方法。

假设以图像为8bit 灰度图进行讨论,f(x,y)表示图像中某点(x,y)的灰度值,x、y 为该点坐标。则该点位置的液晶透过率可表示为:

t (x,y)=f(x,y)/255 (1)

该图像点可被观测到的亮度L(x,y)为背光源发光和液晶透过率的综合效果,可表示为背光亮度b和液晶透过率t (x,y)的近似线性组合:

L(x,y) =b·t (x,y) =b·f(x,y)/255 (2)

根据视觉光效一致性的要求,必须寻找一种方法使像素灰度值在增大(以补偿背光b 变小)的时候尽量不饱和。为达到这个目的,本文首先将图像灰度值范围先限制在一定区间,然后再对直方图进行拉伸,以实现像素灰度值的增大。图像直方图由门限fgl 和fgh 进行裁剪,使图像中的某些点被钳位于fgl 和fgh,该图像的灰度区间限制于[fgl,fgh],背光源调光问题转化为这幅直方图经过裁剪的图像应当如何进行调整,使得它的背光能尽量降低亮度。

显然对固定的失真度,fgl 和fgh 可以有多种取值,这里取值方式应满足公式(3):

min (fgh- fgl ) (3)

这样处理的目的是将图像灰度区间限制在一个最小范围内。

公式(3)实现后,下一步对直方图进行线性搬移,使灰度整体向暗区域移动fgl.这样图像灰度区域由[0,255]区间内的原分布,被压缩在[0,fgh- fgl]区间。

假设背光变暗,此时应对图像进行灰度拉伸,以弥补背光导致的亮度损失。若采取线性拉伸方法,显然拉伸的最大倍数为255/(fgh- fgl),此时像素灰度不会饱和,则背光亮度可由1 降低为(fgh- fgl)/255.根据公式(2),经过处理后的图像在背光调节前后视觉效果不变。

2 硬件和软件实现方案

本实验采用mini2440 开发板进行验证,mini2440是一款低价实用的ARM9 开发板,处理器为三星S3C2440(ARM920T,最高主频可达532MHz)。液晶屏支持黑白、4 级灰度、16 级灰度、256 色、4,096 色STN 液晶显示,尺寸从3.5~12.1in,屏幕分辨率可以达到1,024×768 像素,实验采用了3.5in LED 背光TFT液晶屏。

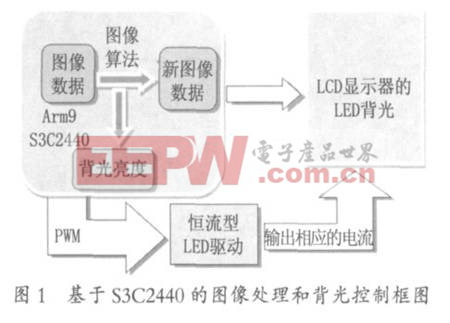

实验中根据图像算法计算图像的灰度值,通过对显示图像的直方图进行裁剪,使之限定在一定范围内,其后进行直方图拉伸,再由计算公式(fgh- fgl)/255 计算出背光源的显示亮度,并控制背光源脉宽调制输出脉冲的占空比,实现背光源LED 的亮度调节。硬件框图如图1 所示。

2.1 LED 背光源驱动设计

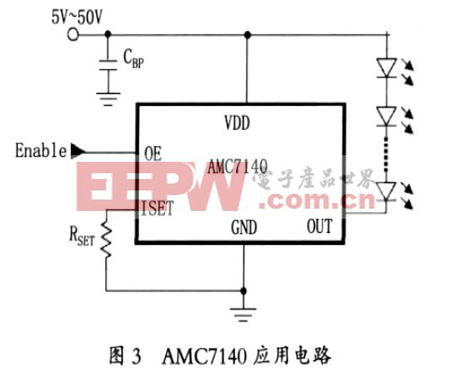

设计采用恒流型LED 驱动,输出电流稳定,保证了背光LED 的亮度恒定,方便通过更改相关的外围电阻来确定输出电流的大小,并具有高灵敏度的开关控制功能,能实现通过PWM 来控制LED 的亮度。

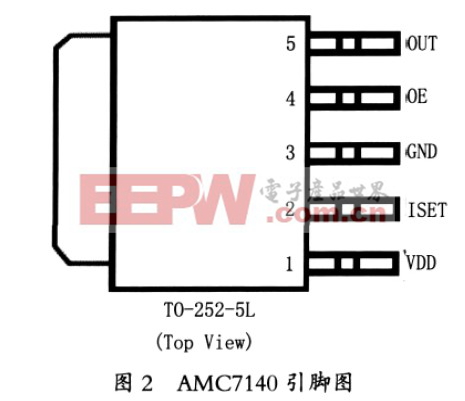

AMC7140 是大功率的LED 恒流驱动芯片,宽电压输入DC 范围为5~50V, 输出电流最大达700mA, 适合驱动1W、3W、5W 的LED 灯,TO- 252- 5L 封装,带PWM CONTROL 端(OE 引脚)。如图2 所示是AMC7140 的引脚图,其中引脚1 是电源输入;引脚2 是输出电流的控制端,通过一个高精度的电阻Rset 接地实现对电流的控制,电流Iset=1.2V/Rset,输出电流Iout=500×Iset;引脚3 接地;引脚4 是PWM 控制端,高电平有效;引脚5 是输出端。AMC7140 的应用电路如图3 所示。

S3C2440 有5 个16bit 定时器。定时器0、1、2、3 有脉宽调制功能(PWM);定时器4 是内部定时器,没有输出引脚;定时器0 有死区发生器,常用于大电流设备中;定时器0、1 共用一个8bit 预脉冲分频器,定时器2、3、4 共用另外一个。每个定时器都有一个时钟分频器,它可以产生5 种分频信号(1/2、1/4、1/8、1/16 和TCLK)。每个定时器模块从自己的时钟分频器获取时钟信号,时钟分频器从相应的8bit 预脉冲分频器中获取时钟。这个8bit 预脉冲分频器是可编程的,并依据TCFG0 和TCFG1 寄存器中的值对PCLK进行分频。定时器被使能之后,定时器计数缓冲寄存器(TCNTBn)中的初始值就被加载到递减计数器中, 定时器比较缓冲寄存器(TCMPBn) 中的初始值就被加载到比较寄存器中,以便与递减计数器的值进行比较。这种TCNTBn 和TCMPBn 的双缓冲特点使得定时器在频率和占空比变化时输出的信号更加稳定。每个定时器都有一个自己的时钟驱动的16bit 递减计数器,当计数器减到0 时,产生一个定时器中断请求,以通知CPU 定时器操作完成,同时定时器计数缓冲寄存器的值被再次自动加载到递减计数器继续下次操作。然而,如果在正常模式下清除定时器TCONn 的使能位,TCNTBn的值将不再加载进计数器,TCNTBn 的值常用于PWM.当递减计数器的值等于比较寄存器的值,定时器控制逻辑改变输出电平,因此,比较寄存器决定了PWM 输出的开启和关闭。

设置一个定时器,首先初始化TCNTBn 和TCMPBn,在初始化定时器时,主要设定以下几个寄存器(以定时器0 为例):

分频器相关文章:分频器原理

评论