Niosll和USB接口的高速数据采集卡设计

引 言

本文引用地址://m.amcfsurvey.com/article/151090.htm随着现代工业生产和科学研究对数据采集的要求日益提高,在瞬态信号测量、图像信号处理等一些高速、高精度的测量中,都迫切需要进行高速数据采集(如雷达信号分析、超音波信号分析);而进行数字处理的先决条件是将所研究的对象数字化,因此数据采集与处理技术日益得到重视。在图像信号处理、瞬态信号检测、工业过程检测和监控等领域,更是要求高速度、高精度、高实时性的数据采集与处理技术。现在的高速数据采集处理卡一般采用高性能数字信号处理器(DSP)和高速总线技术的框架结构。DSP用于完成计算量巨大的实时处理算法,高速总线技术则完成处理结果或者采样数据的快速传输。DSP主要采用TI和ADI公司的产品,高速总线可以采用ISA、PCI、USB等总线技术。其中PCI卡或ISA卡安装麻烦,价格昂贵,受计算机插槽数量、地址、中断资源的限制,可扩展性差,在一些电磁干扰性强的测试现场,无法专门对其做电磁屏蔽,易导致采集的数据失真。通用串行总线USB是为解决传统总线不足而推广的一种新型的通信标准。该总线接口具有安装方便、高带宽、易于扩展等优点,已逐渐成为现代数据发展趋势。基于USB的高速数据采集卡充分利用USB总线的上述优点,有效地克服了传统高速数据采集卡的缺陷。

1 系统硬件设计

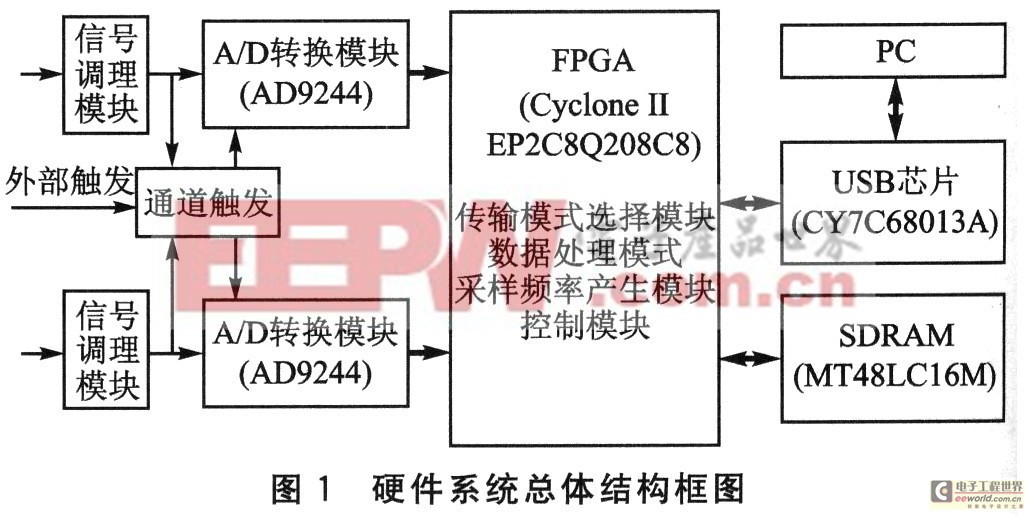

本系统主要是基于USB2.O的S1ave FIFO模式,在FPGA控制下完成双通道、不同速率的数据的采集和发送,全兼容USB2.O总线接口标准,其数据的采样率可高达65 Msps;适用于较高速动态信号的实时记录采集,其硬件系统总体结构框图如图1所示。

该系统主要由信号调理模块、A/D转换模块、触发模块、基于FPGA的主控模块、USB收发控制模块、片外存储器及其他辅助电路组成。调理电路与A/D转换器,将传感器采集的模拟信号进行相关的信号调理后送入AD9244芯片转换为数字信号。处理后的数据送往FPGA主控模块,根据相关的控制信息,选择通过直接传输给上位机,或者先存储在外部SDRAM,然后经过相关的数字处理后再传输给上位机。

2 系统模块介绍

2.1 USB2.0专用微处理器CY7C68013A

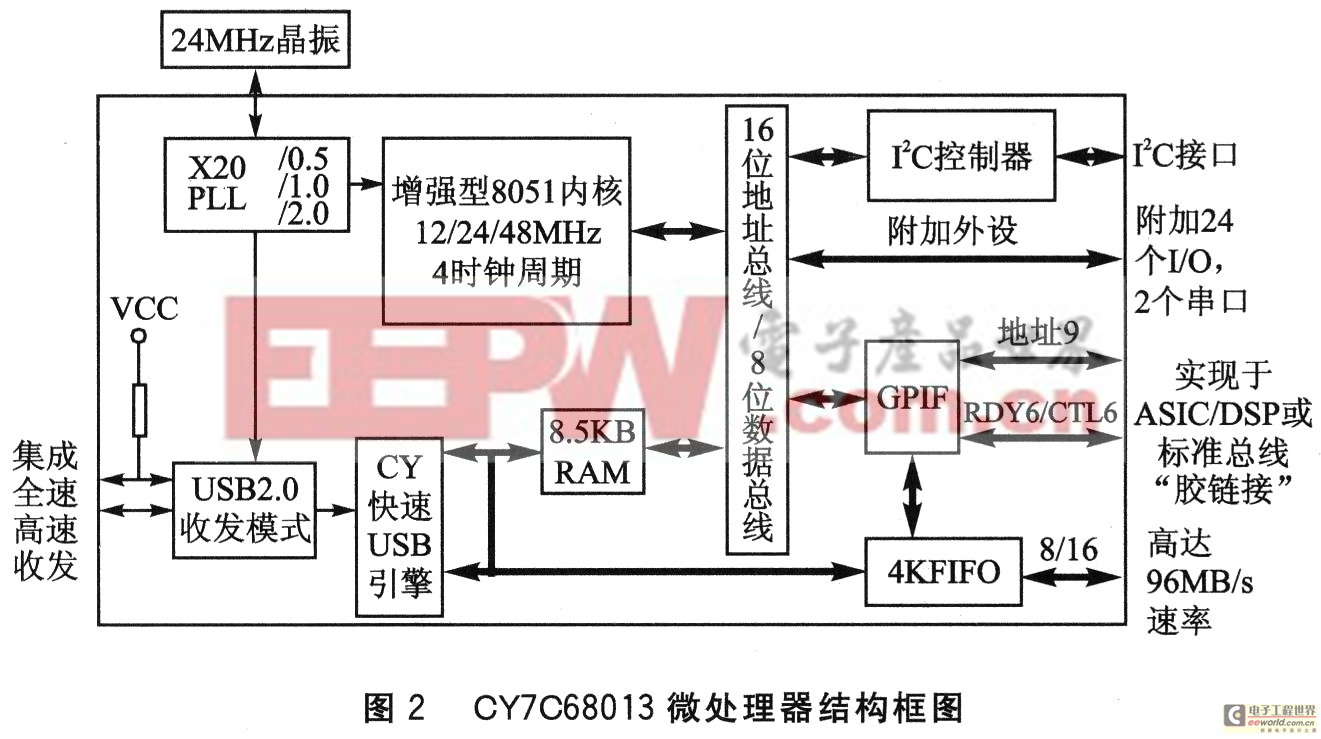

CY7C68013A是Cypress Semiconductor公司生产的一款集成USB2.O的微处理器。它有3种封装形式——56SSOP、100TQFP和128TQFP,其结构框图如图2所示。

CY7C68013集成了USB2.O收发器、SIE、增强的8051微控制器和可编程的外围接口部件。其SIE可在全速(12 Mb/s)和高速(480 Mb/s)两种模式下运行,同样可以使用内部RAM来进行程序和数据的存储。GPIF和Master/Slave端口FIFO为ATA、UTOHA、EPP、PCM—CIA和DSP等提供了简单和无需附加逻辑的连接接口。其编程可以根据设计的需要进行,不需要CPU的干预,只需通过CPU的一些标志和中断即可进行通信。CY7C68013共有7个输入输出端口:EP0、EPlOUT、EPlIN、EP2、EP4、EP6、EP8,其中EP2、EP4、EP6、EP8可以分别被配置为批量/中断/同步传输模式,传输方向均可配置为I/O,端口EP2、EP6的缓冲区大小可编程为512或1 024字节,深度可编程为2/3/4倍大小;端口EP4、EP8的缓冲区大小固定为512字节,深度为2倍,采用不同的配置方式,可实现特定带宽和速率要求的数据传输。

评论