基于ADSP-TS201S的多DSP并行系统设计

5 系统软件设计

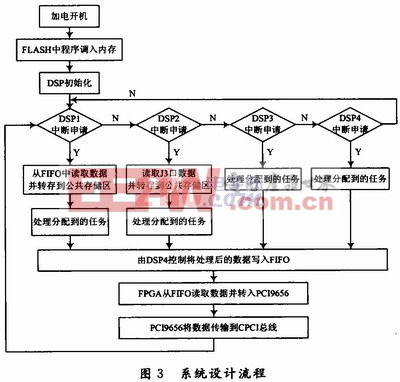

由于系统硬件是基于DSP+FPGA的结构,相应的软件也分为两个功能模块。FPGA主要完成整个系统的数据传输逻辑控制,因此FPGA具体的处理流程嵌套在DSP的信号处理流程中。4片DSP主要完成信号的处理,大致的系统设计流程如图3所示。本文引用地址://m.amcfsurvey.com/article/151299.htm

4片DSP并行工作时,总线仲裁策略指定DSPl为主处理器,由它完成系统的初始化、数据程序配置、与CPCI工控机主机通信等,并参与运算工作。当系统 接收到数据时,首先判断信号的传输方式,若是并行信号,由FPGA进行相应处理后写入FIFO中,同时通过外部中断告知DPS-l,随即DSPl发出中断 申请,总线仲裁令DSP1获得总线控制权,读取FIFO中的数据并转存至公共存储区;然后DSP1通过LINK口与其他DSP通信,进行任务分配,其他 DSP依次循环获得总线控制权,读取数据进行处理然后再存入存储区;最后,由DSP4控制将存储区里的数据写入FIF-O,同时通知FPGA读取并完成时 序转换后传输到PCI9656,由PCI9656将数据传输到CPCI总线,完成这一帧数据的处理。若系统接收到的数据是由J3口传输来的串行信号,则先 由DSP2发出中断申请,总线仲裁令DSP2获得总线控制权,将接收到的数据转存至公共存储区;然后通过同样的方式在4片DSP间进行任务分配和处理,由 DSP4写入FIFO,最后由FPGA和PCI9656联合将数据传输到CPCI总线,完成串行信号的处理。

6 结语

本文介绍了一种基于PFGA的多DSP并行处理系统的设计,重点对DSP并行结构设计进行了分析,并介绍了FPGA设计和外部设备接口设计。实际应用表 明,该多DSP并行处理系统应用于宽带雷达信号处理时,能够满足任务中的各项指标,还能完成设计外的其他功能,并且易于控制,稳定可靠。本文提供的系统设 计方案能够为处理宽带雷达信号的其他研究人员提供一定的参考。

评论