基于DSP的1553B总线系统设计与实现

摘要:在研究1553B总线协议特点的基础上,提出了一种基于DSP的1553B总线接口设计方案.详细描述了硬件电路的实现及软件驱动程序的编写。在电路中采用DSPTMS320F2812为核心处理单元。BU-64843为1553B协议执行元件,采用FPGA实现地址译码和逻辑控制功能。为了保证1553B总线消息处理的实时性,直接由下位机DSP控制1553B协议芯片,负责消息的读取、处理、写入和1553B协议芯片的初始化,通过对BU-64843寄存器的配置,使系统工作在BC/RT/MT模式。通信协议处理模块严格按照通信协议收发周期性消息,时间误差精度小于1μs。

关键词:1553B;总线接口;DSP;FPGA;TMS320F2812

航空电子综合化是一种在苛刻的空间限制条件下,对密集型的航空电子子系统集合进行信息综合和功能综合的技术。以MIL-STD-1553B为代表的子系统联网接口标准构成了目前航空电子综合系统中信息交换的主干道。1553B总线接口电路是实现航空电子综合化系统的关键部件,其作用是在1553B总线与现有的其他总线技术之间搭建一座桥梁,使得不同制式的信息流能够实时、准确地进行相互转换。在1553B总线接口的研制过程中,复杂而苛刻的环境对中央处理器的实时性与可靠性提出了很高的要求,而DSP芯片以其优良的高速性能为中央处理器的选择提供了一个较为理想的解决方案。

随着MIL-STD-1553B总线协议标准的颁布。许多公司开发了总线与CPU之间的硬件接口芯片。在实际的1553B总线工程中使用最为广泛的是DDC公司生产的接口芯片。这些芯片完全实现了1553B总线的电气特性协议,而且与CPU或存储器连接非常简单。本文探讨基于TMS320F2812(以下简称F2812)和DDC公司的BU-64843协议芯片的1553B总线接口的硬件设计和软件驱动编写要点。

1 1553B总线

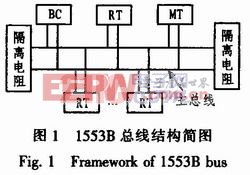

1553B总线是一种时分制指令/响应式多路传输数据总线,具有很高的可靠性和良好的实时性。1553B总线由4种基本硬件组成:传输介质、总线控制器(BC)、远程终端(RT)、总线监视器(MT)。

1553B总线采用异步、半双工方式传输,传输速率1 MB/s。1553B总线传输协议规定的传输过程为:BC向某一终端发送一个接收/发送指令,RT在规定的响应时间内发回一个状态字并执行消息的接收/发送。在操作过程中BC始终掌握总线的控制权,总线上任何时候只有一个BC,但可以最多挂31个RT或MT。在总线的数据传输过程中,MT按要求监视总线上的数据,并将这些数据输出或者存盘以便实时地监测这些数据的传输状态或便于后续分析。1553B采用双冗余总线,有2个传输通道,保证了良好的容错性和故障隔离。如果当前总线的数据传输出现错误或故障,数据可以自动从冗余总线上传输。1553B总线的传输介质为屏蔽双绞线。其总线结构简图如图l所示。

2 系统设计方案

该系统以F2812为控制核心,与外围辅助电路构成微计算机系统;由BU-64843协议芯片完成1553B总线的功能。BU-64843提供了丰富的资源。为软件的设计提供了极大的灵活性和可靠性;控制和译码信号利用FPGA实现,FPGA器件电路连接简单,使用方便,使用功能强大的VerilogHDL语言编程,可提高系统的维护性和扩展性。

F2812负责消息的读取、处理、写入和BU-64843协议芯片的初始化。通过对BU-64843的相关寄存器进行相应的配置,就可以使本接口卡工作在BC模式、RT模式或MT模式。接口卡在BC模式下实现1553B总线消息的接收,BU-64843协议芯片每接收完一个消息,就向F2812发送一次中断申请,由F2812响应中断并从相应的RAM区读取接收到的消息进行相应处理,F2812同时完成与上位机的通讯,并把接收到的数据发送出去。与上位机的通讯是利用F2812的串行通信接口(SCI),本系统采用MAX485实现的。

评论