基于ARM的可定制MCU可承担FPGA的工作

如今的产品生命周期可能短至六个月,因此在这种情况下要想取得定制ASIC的低成本、低功耗和高性能优势几乎是不可能的。定制ASIC的设计周期通常要一年左右,这通常要比终端产品的生命周期还要长。另外,标准单元ASIC还具有NRE费用(非重复工程成本),对于基本的0.13微米设计,该成本约为30万美元,而对于具有复杂IP内容的90nm设计将超过100万美元。因而当每年的批量小于10万片时,从经济角度看就不具有可行性。

本文引用地址://m.amcfsurvey.com/article/151377.htm为此人们研发出了平台化或结构化ASIC,它们具有预设计的IP块和可编程的ASIC门,可显著降低成本并缩短设计周期。这种方案将设计周期从一年甚至更长的时间缩短到几个月,还将NRE成本降低到大约15万美元,不过与门阵列相关的较大尺寸使得单片成本过高而无法补偿NRE。

利用现成的标准微控制器来实现设计通常会较快且具有较高的成本效益,许多微控制器都是系统级芯片(SoC),能够提供大量的网络功能和人机接口功能,例如LCD控制器和相机接口。这些现成的SoC常常具有所有功能,性能高且成本低,采用基于单元的ASIC即可实现。但是, 需要硬件加速的一些设计中要求一些高强度运算的功能,如Turbo编码、GPS环形解调器和图形处理等,它们都需要用硬件实现。未来发展趋势是利用FPGA来实现这些DSP功能。由于工艺技术的进步,这种设计的成本将明显降低,而且几乎有完全取代平台ASIC。

不过,FPGA也有一些缺点,最显著的是功耗高,执行速度慢,FPGA中IP的安全性也相对较差。尽管其成本下降很快,但当批量达到1万片时,其批量成本就不再下降了。因此FPGA还比较贵。

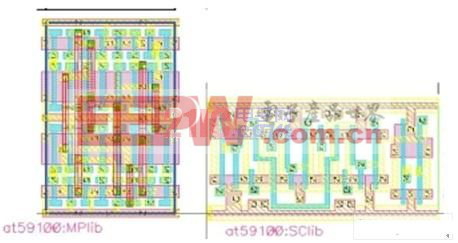

目前有种新的ASIC技术,它采用一种金属-可编程的单元结构(MPCF),所实现的硅片效率与单元ASIC相当(在130nm工艺上为170K-210K门/mm2)。例如,在130nm工艺节点,利用MCPF实现一个D触发器(DFF)所用的硅片面积与标准单元相比几乎相同(图1:用130nm MPCF和130nm 标准单元实现的D触发器)。

目前正在利用MPCF技术开发可定制的微控制器,它不仅具有单元ASIC的超低单片成本优势,还具备结构化ASIC的低NRE和不到两个月设计周转期的优点。基本上,具有SoC级集成度的现有MCU结合金属化可编程单元结构就可用来实现可定制的SoC平台。

作为这种可定制微处理器的一个例子,它采用了基于200 MHzARM926EJ-S的现有MCU,带有用于确定性处理且均为16 Kbytes的紧耦合程序和数据高速缓存,32 Kbytes的附加SRAM,32 Kbytes的ROM以及支持网络、数据传输、人机接口的外设,并增加了一个等效于28K 或 56K FPGA LUTs (250K 或 500K 可布线 ASIC门)的金属化可编程块(MP)。(图2- AT91CAP9方框图)。器件上已有的外设包括USB 主机和器件、10/100 以太网MAC、LCD控制器、用于连接CAN、MCI和SPI总线的图像传感接口。

图1:用130nm MPCF和130nm 标准单元实现的D触发器。

评论