基于NiosII处理器的通用AD IP核的设计与实现

2.2 FIR滤波器模块的设计

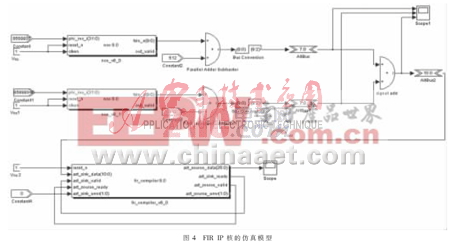

在实际应用的数据采集系统中,往往需要对外界模拟输入信号进行滤波,以提取信号中有用的信息。在本设计中这部分的功能是由FIR滤波器模块来完成的。FIR滤波器模块采用Altera公司提供的FIRIP核来实现,通过Simulink软件中的DSP Builder工具对其进行仿真并最终可以生成底层HDL代码。由于TLC549的最高采样频率为40 kHz,本文设计了一个低通滤波器,它的采样频率为40 kHz,3 dB截止频率为100 Hz。在Simulink软件中建立的FIRIP核的仿真模型如图4所示。本文引用地址://m.amcfsurvey.com/article/151966.htm

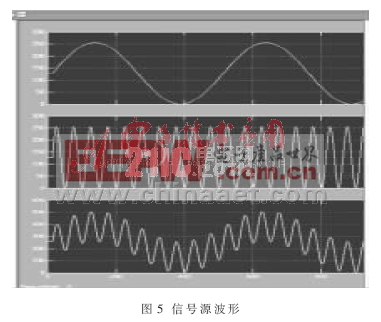

图4中nco_v8_0模块和nco_v8_1模块是2个数控振荡器,分别用于产生100 Hz和1 kHz的正弦信号,signal add模块是并行加法器,它将两路正弦信号进行叠加并将和信号输出。fir_compiler_v8_0模块是FIRIP核,它将signal add模块输出的和信号作为输入,并将数字滤波的结果输出到示波器进行显示。仿真结果如图5和图6所示。

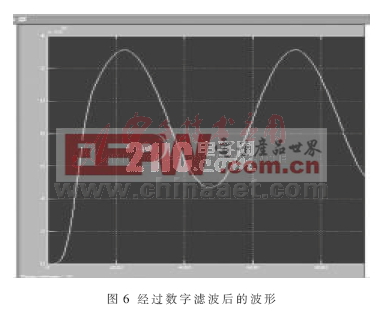

由图5可以看出:第1路是频率为100 Hz的正弦信号,第2路是频率为1 kHz的正弦信号,第3路是前两路信号的叠加。图6中显示的是经过数字滤波后的波形,可以看出只有100 Hz的频率分量存在,1 kHz的信号被滤除了,从而完成了对FIR IP核的功能验证。通过图4中的Signal Compiler工具可以完成该FIR IP核的底层HDL代码的生成。

FIR滤波器模块采用Altera公司提供的FIR IP核来实现,具有高性能、可配置、可重用等特点。设计者只需根据整个系统的需求以及所选用AD芯片的采样速率等参数确定滤波器的类型与系数,并对该IP核进行参数化、实例化,即可完成针对该款AD芯片的FIR滤波器模块的设计。因此这部分的设计对于不同的AD芯片是相对独立的,具有很好的通用性。

2.3 FIFO缓存模块的设计

为了连续和正确地采集数据,实现无缝缓冲,本设计利用了FIFO做数据缓存。由于TLC549是8位的AD芯片,故本设计采用1个512×8 bit 的FIFO来存储采样的数据。当FIFO中的数据存满时,它会向Nios II CPU产生一个中断信号。顶层应用程序可以通过中断服务程序将FIFO中的数据读到内存中进行处理。这样既不会造成数据的丢失,同时可以保证CPU较高的效率,很好地解决了上述的速度不匹配的问题。

FIFO缓存模块的设计对于不同的AD芯片是相对独立的,设计者只需根据所选用AD芯片的精度、采样速率、时钟速率等参数确定FIFO缓存的位宽和深度,并对FIFO进行参数化、实例化,即可完成针对该款AD芯片的FIFO缓存模块的设计,因此具有很好的通用性。

评论