基于SoPC的自感知运动图像采集系统设计

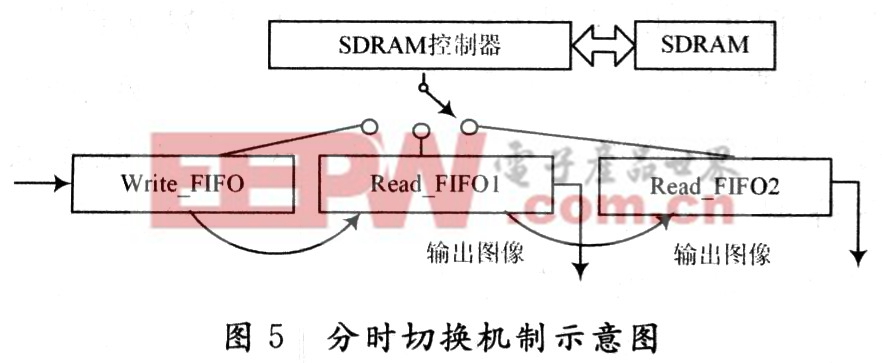

2.2.2 帧存分时切换机制

Write_FIFO,Read_FIFO1和Read_FIFO2都是16 b位宽,而SDRAM只有16 b的数据位宽,三个FIFO都要访问SDRAM,这就涉及到相互竞争的问题,在同一时刻只能有一个访问SDRAM。为此需要设计一个分时切换机制。由于SDRAM的操作时钟为100 MHz,而采集像素时钟为25 MHz,经过抽样后时钟频率更是大大降低。在一次采集周期内,SDRAM完全可以和三个FIFO的接口轮流切换,从而不会影响采集的速度。

如图5所示,其工作过程为:

(1)图像经格式转换模块输出,写入Write_FIFO的输入端口。

(2)当控制电路检测到Write_FIFO中读出端的数据量大于256(三个FIFO容量均为512 word)时,产生写命令,并拥有写互斥锁。SDRAM控制器接到命令,以100 MHz时钟将256个数据写入SDRAM。

(3)Write_FIFO输出256个数据后,读出端的数据量小于256,并且由于Read_FIFO1中初始状态的输入端数据小于256,Read_FIFO1拥有读互斥锁,产生读命令,SDRAM控制器接到命令,以100 MHz时钟将256个数据读出,并写入Read_FIFO1。

(4)当Read_FIFO1收到256个数据,其输入端数据大于256,并且由于Read_FIFO2中初始状态的数据小于256,Read_FIFO2拥有读互斥锁,产生读命令,SDRAM控制器将256个数据读出,并写入Read_FIFO2。

(5)这样就完成了一次操作,之后就是循环操作。地址信号也是由控制电路产生,每经过一次读写,地址增量为256,这样就可以保持信号的连续性。

(6)Write_FIFO在一定周期内向SDRAM中连续写入两帧连续图像;Read+FIFO1根据SDRAM中的地址读取其中的一帧图像数据;而Read_FIFO2读取另一帧图像数据。

通过这个机制,三个FIFO中始终都有数据,不会发生读空、写满情况,使得存储器两端的数据读/写方便,只要在write FIFO的输入端和Read―FIF01、Read FIFO2的输出端进行操作就行,在时钟的上升沿将数据写入或输出,实现了异步方式。

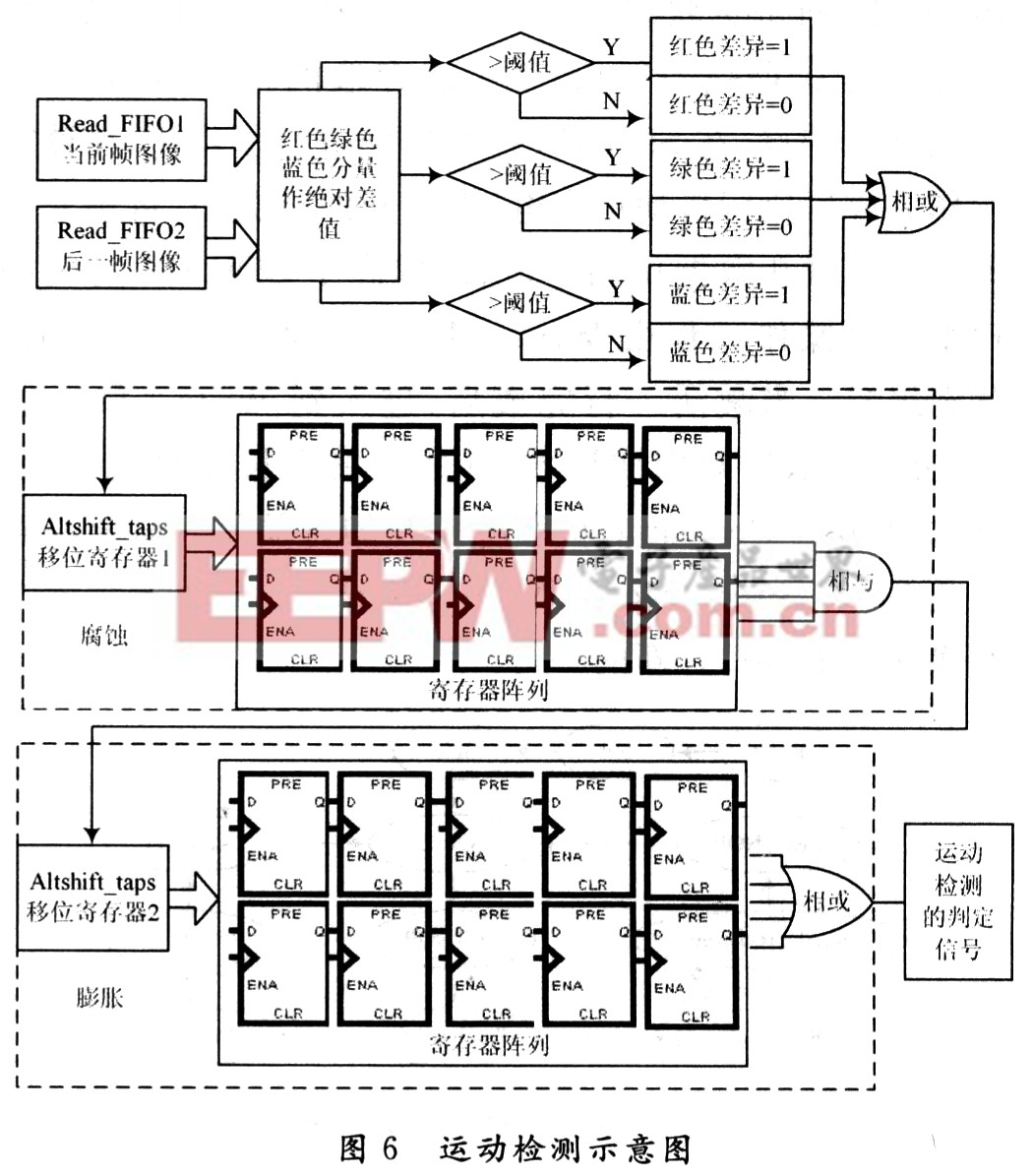

3 运动检测模块

该模块采用帧间差分法,其基本原理是将连续的两帧或几帧的图像对应的像素值相减,在环境亮度变化不大的情况下,如果对应像素值相差很小,则认为此处景物是静止的,如果图像区域某处的像素值变化很大,可认为这是由于图像中运动物体引起的。其算法实现简单,能够适应各种动态环境,稳定性较好。

设计中对相邻两帧图像的每个像素RGB分量分别取绝对差值。当绝对差值大于阈值时(这里取经验值16),就认为存在差异,如果做比较的两个像素的RGB分量只要有一个分量有差异,则令此点的数值为1,这样就得到一幅320×240像素大小的二值差值图像。然后传统处理方法是统计值为1的点的个数,如果其数量超过预设值,就认为两幅图像有差异。这种方法设计简单,但是准确率还不够高,为此该设计提出了一种改进的算法,引入了图像处理常用的两种操作腐蚀和膨胀。腐蚀与膨胀是一对逆运算,如果先腐蚀再膨胀,便构成了开运算。一般来说,开运算能够去除孤立的小点,毛刺和小桥(即连通两块区域的小点)。而总的位置和形状不变。

对上述二值图像进行开运算处理,可以消除小颗粒的噪声的干扰,从而尽可能降低误判和漏判。

设计流程如图6所示,通过调用ALTSHIFTTAPS IP核,并利用输出TAPS,构建一个11×11像素大小的图块作为结构元素,然后腐蚀:

(1)用11×11的结构元素,扫描图像的每一个像素;

(2)用结构元素与其覆盖的二值图像做“与”操作;

(3)如果都为1,结果图像的该像素为1,否则为0。

接着再将上述结果作为第二个ALTSHIFTTAPS的输入,再次构建11×11个像素的结构元素,然后进行膨胀处理:

(1)用11×ll的结构元素,扫描图像的每一个像素;

(2)用结构元素与其覆盖的二值图像做“或”操作;

(3)如果都为0,结果图像的该像素为0,否则为1。

最后得到运动判定信号DETECT,并用这个信号控制数据写入过程,一旦判定信号为1,就启动后续的图像存储过程。

评论