基于SoPC的自感知运动图像采集系统设计

(1)接口电路模块。在各种存储设备中,SD卡不仅小巧,而且功耗很低,另外市面上常见SD卡的容量可达到2 GB以上,因此非常适合用于对体积和功耗要求严格的嵌入式图像存储。该设计选用APACER公司的一款高速SD卡(传输速率为150X,容量4 GB)。为了增强系统的可扩展性,该设计在FPGA芯片中嵌入Altera公司新近推出的第二代高性能NiosⅡ软核处理器,其处理能力超过200 MIPS,并在NiosⅡ中完成SD卡驱动程序设计。前端的采集缓存电路与NiosⅡ系统之间的数据和控制信号由定制的接口模块完成。

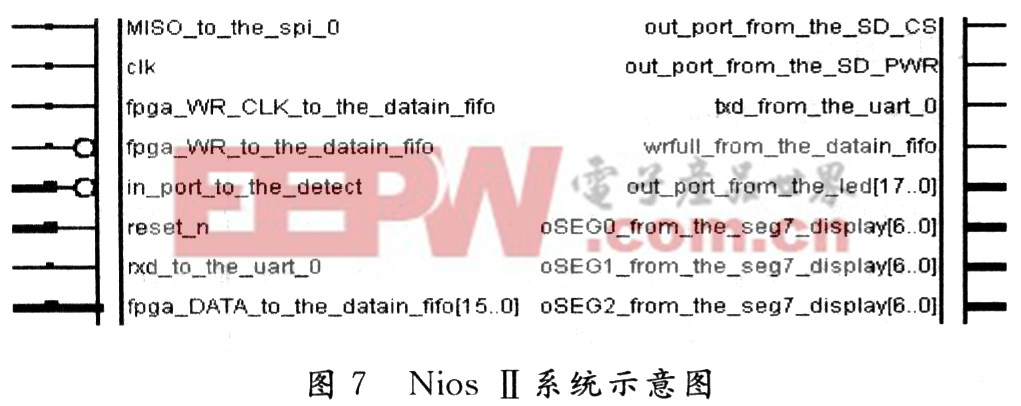

定制IP核DATAIN_FIFO是在SoPCBuilder环境下完成(如图7所示),DATAIN_FIFO写端口的时钟信号、写请求信号同步于SDRAM控制模块的ReadFIFO1,而DATAIN_FIFO的读端口的时钟、读请求信号则由CPU控制。以上信号除了waitrequest之外,都由Avalon交换结构自动产生和控制。waitrequest信号可以直接连接到异步FIFO的rdempty输出,当FIFO读空之后,waitrequest有效,插入等待周期,一直到从端口的数据准备好才输出readdata。开始和结束采集控制信号由DETEcT信号和DMA中断信号决定,确保采集到的数据刚好为一帧320×240图像。

由于NiosⅡ系统提供了成熟的SPI接口,所以设计中采用SPI总线协议模式来读写SD卡。因为MMC卡在复位阶段要求SPI的时钟频率要小于等于400 kHz,为了提高读写速度,本设计设计的接口不再兼容MMC卡,其设置SPI的SCK引脚的输出频率在数据传输时设为25 MHz。本文引用地址://m.amcfsurvey.com/article/152285.htm

(2)BMP图像文件创建程序。为提高程序运行速度。并考虑到该系统的实际需要,程序只实现了写BMP图像文件功能。程序主要由SD卡操作驱动接口函数和文件系统层组成。

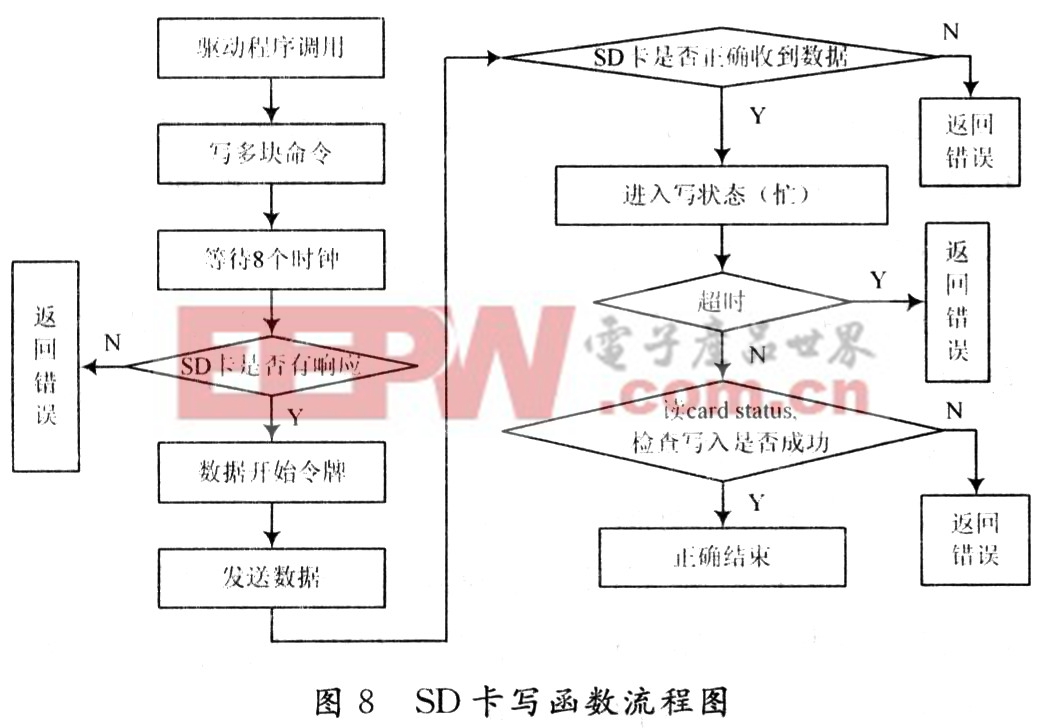

驱动函数目的是为文件系统层提供所需的SD卡初始化函数和SD卡写多块数据函数。图8是SD卡写函数流程图示意图。当写函数接收到主程序的写文件指令后,就向SD卡发送多块写命令,卡将发送给主机一个应答令牌,并且等待主机发送一个发送数据块来,当应答R1为0时,说明可以发送数据,块大小设置为512 B。数据块之后附有16位的CRC校验,因为CRC校验计算占用了很大部分发送的时间,该系统采用自定义用户指令对这部分进行了加速处理。

要使写入SD卡的数据在装有Windows或Linux操作系统的上位机中得到正确访问,需要在SD卡上创建它们支持的文件系统。考虑到FAT12目前已经很少使用,在此设计的文件系统只支持FAT16和FAT32。并且将整个卡作为一个分区处理。

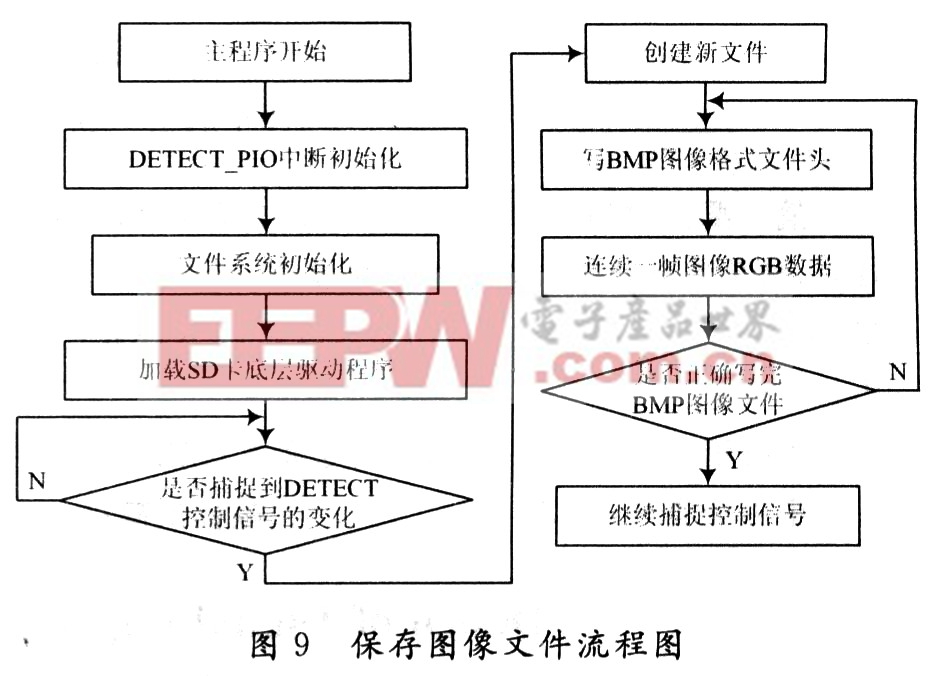

图9是系统的软件工作主要流程图。在主程序中,系统启动后,先进行初始化操作,包括中断初始化、文件系统初始化和SD卡底层驱动的初始化。随后系统进入主循环等待状态,一旦检测到DETECT_PIO电平的变化就暂停SDRAM数据写入,以防SDRAM缓存的图像数据被覆盖,同时根据当前的时间创建一个BMP格式的文件,然后往里填写文件头和文件信息头,随后连续写一帧RGB数据。文件创建完毕后系统继续处于检测等待状态,并恢复SDRAM数据写入。

5 系统评价

该设计在自制核心实验板上(见图10)进行了软、硬件仿真和调试,调试环境参数设定如下:采集时钟频率为25 MHz,NiosⅡ时钟频率为100 MHz、每帧图像大小为320×240像素。调试结果如下:系统采集速度在60帧/s左右。对五米之内场景动态变化的响应时间在5 ms左右,SD卡保存单帧图像时间约为9 s(每帧图像数据量是153 600 B),连续工作一个星期无任何故障发生。结果表明该系统图像采集和处理速度超过一般的以软件实现为主的嵌入式图像采集方案(如ARM处理器系统)。由于核心处理器采用单芯片方案,采集系统比较稳定,同时其功耗大大低于多芯片方案。

6 结 语

在此提出一种基于SoPC技术的图像检测、采集和储存的一体化单芯片控制新型系统集成方案,并实现了原型系统,该系统的主要特点是处理速度快、功耗低、稳定可靠。

该设计可以在进一步工作中移植嵌入式操作系统μCLinux,以实现复杂的多任务操作。因此该设计既可作为独立的解决方案应用于便携式原位观测系统中,同时以其良好的扩展性,也可作为一个子系统应用于大型图像处理系统的前端部分。

评论